## HW4

氏名:津波古正輝

学籍番号:075739A

提出日:12月2日(火曜日)

1)与えられたALU記述に対して以下をレポートする。

SIROCCOでの正常動作波形、展開前の回路で、速度最小での回路図、面積、クリティカルパス遅延、クリテイカルパスの入力ピンと出力ピン。展開後の回路で、速度最小での回路図、面積、クリティカルパス遅延、クリテイカルパスの入力ピンと出力ピン。展開による合成結果の差の考察。

- 2) 記述を変更して4ビットと16ビットの同一機能のALUを設計し、

- 2-1) 制約なしで合成し、4ビット、8ビット、16ビットALUのビット幅と回路面積、およびビット幅と回路速度の関係を調べよ。

- 2-2) 最小速度で合成し、

4 ビット、8 ビット、1 6 ビットALUのビット幅と回路面積、およびビット幅と回路速度の関係を調べよ。

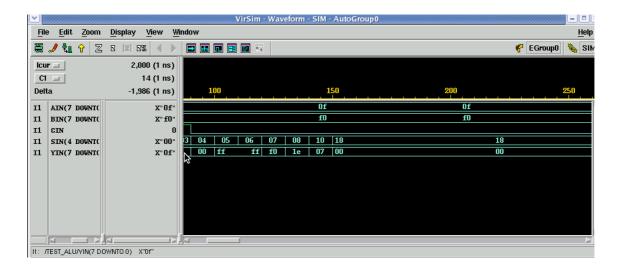

# 1):SIROCCO での正常動作波形

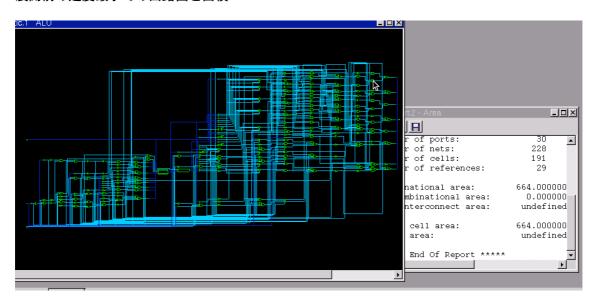

## 展開前の速度最小での回路図と面積

クリティカルパス遅延、クリテイカルパスの入力ピンと出力ピン

| Point                                      | Incr | Path    |

|--------------------------------------------|------|---------|

| input external delay                       | 0.00 | 0.00 r  |

| Sel[1] (in)                                | 0.00 | 0.00 r  |

| U130/Z (B4IP)                              | 0.04 | 0.04 f  |

| U129/Z (NR2I)                              | 0.57 | 0.61 r  |

| U128/Z (ND2I)                              | 0.12 | 0.73 f  |

| U184/Z (ND2I)                              | 0.25 | 0.98 r  |

| U187/Z (IVI)                               | 0.17 | 1.16 f  |

| U300/Z (AO3P)                              | 0.68 | 1.84 r  |

| r25/B[0] (ALU_DW01_addsub_1)               | 0.00 | 1.84 r  |

| r25/U122/Z (ENI)                           | 0.58 | 2.42 f  |

| r25/U105/Z (NR2I)                          | 0.57 | 2.99 r  |

| r25/U104/Z (ND2I)                          | 0.26 | 3.26 f  |

| r25/U103/Z (IVI)                           | 0.29 | 3.55 r  |

| r25/U38/Z (NR2I)                           | 0.20 | 3.76 f  |

| r25/U100/Z (ND2I)                          | 0.30 | 4.05 r  |

| r25/U94/Z (ENI)                            | 0.62 | 4.67 r  |

| r25/SUM[2] (ALU_DW01_addsub_1)             | 0.00 | 4.67 r  |

| sub_0_root_add_40/A[2] (ALU_DW01_sub_0)    | 0.00 | 4.67 r  |

| sub_0_root_add_40/U14/Z (ND2I)             | 0.12 | 4.79 f  |

| sub_0_root_add_40/U15/Z (IVI)              | 0.24 | 5.03 r  |

| sub_0_root_add_40/U69/Z (ND2I)             | 0.12 | 5.15 f  |

| sub_0_root_add_40/U68/Z (AN2I)             | 0.64 | 5.79 f  |

| sub_0_root_add_40/U63/Z (ND2I)             | 0.25 | 6.04 r  |

| sub_0_root_add_40/U51/Z (ND2I)             | 0.12 | 6.16 f  |

| sub_0_root_add_40/U50/Z (ND2I)             | 0.25 | 6.41 r  |

| sub_0_root_add_40/U49/Z (ENI)              | 0.48 | 6.89 f  |

| sub_0_root_add_40/DIFF[5] (ALU_DW01_sub_0) | 0.00 | 6.89 f  |

| U298/Z (MUX31LP)                           | 1.25 | 8.14 r  |

| U139/Z (IVI)                               | 0.18 | 8.32 f  |

| U306/Z (ND2I)                              | 0.29 | 8.61 r  |

| U305/Z (AO3P)                              | 0.50 | 9.11 f  |

| U270/Z (ND2I)                              | 0.25 | 9.36 r  |

| U272/Z (AN2I)                              | 0.39 | 9.75 r  |

| U273/Z (AO7P)                              | 0.28 | 10.03 f |

| Y[4] (out)                                 | 0.00 | 10.03 f |

| data arrival time                          |      | 10.03   |

面積:664

クリティカルパス:10.3

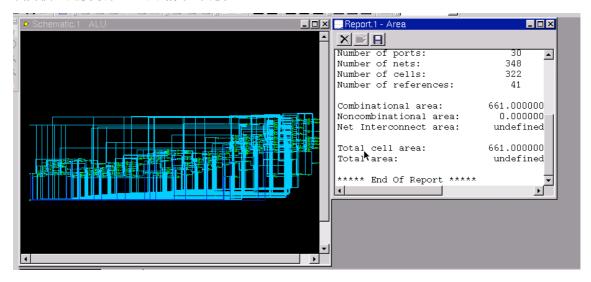

#### 展開後の速度最小での回路図と面積

## クリティカルパス遅延、クリテイカルパスの入力ピンと出力ピン

| Point                | Incr | Path            |  |

|----------------------|------|-----------------|--|

| input external delay | 0.00 | 0.00 r          |  |

| Sel[0] (in)          | 0.00 | 0.00 r          |  |

| U313/Z (B4IP)        | 0.05 | 0.05 f          |  |

| U312/Z (NR3P)        | 1.09 | 1.14 r          |  |

| U429/Z (NR2I)        | 0.24 | 1.38 f          |  |

| U358/Z (AO3P)        | 0.68 | 2.06 r          |  |

| U419/Z (ENI)         | 0.41 | 2.47 r          |  |

| U450/Z (NR2I)        | 0.24 | 2.72 f          |  |

| U447/Z (AO4P)        | 1.24 | 3.96 r          |  |

| U452/Z (AN2I)        | 0.49 | 4.45 r          |  |

| U334/Z (AO4P)        | 0.44 | 4.89 f          |  |

| U384/Z (ND2I)        | 0.33 | 5.22 r          |  |

| U357/Z (EON1P)       | 1.18 | 6.41 r          |  |

| U279/Z (ND2I)        | 0.20 | 6.61 f          |  |

| U257/Z (IVI)         | 0.29 | 6.89 r          |  |

| U323/Z (AO4P)        | 0.44 | 7.33 f          |  |

| U454/Z (AN2I)        | 0.69 | 8.02 f          |  |

| U152/Z (AO4P)        | 1.08 | 9.10 r          |  |

| U378/Z (ND2I)        | 0.19 | 9.29 f          |  |

| U151/Z (EO1P)        | 1.18 | 10.47 r         |  |

| U383/Z (ENI)         | 0.53 | 11.00 f         |  |

| U404/Z (ND2I)        | 0.25 | 11.26 r         |  |

| U310/Z (EON1)        | 1.18 | 12.44 r         |  |

| U397/Z (ENI)         | 0.42 | 12.86 f         |  |

| J396/Z (ENI)         | 0.48 | 13.34 f         |  |

| J144/Z (MUX31LP)     | 1.25 | 14.59 r         |  |

| J268/Z (AO3)         | 0.68 | 15.27 f         |  |

| U415/Z (ND2I)        | 0.25 | 15.52 r         |  |

| J270/Z (AO3)         | 0.43 | 15.9 <b>≨</b> f |  |

| Y[6] (out)           | 0.00 | 15.96 f         |  |

| data arrival time    |      | 15.96           |  |

面積:661

クリティカルパス:15.96

## 考察:

面積はあまり変化していない。クリティカルパスは展開すると遅くなっている。 どうやら展開すると遅くなるようである。面積が大きいものを展開すると、ク リティカルパスは遅くなるようだ。では、逆(面積が小さい)のパターンはどう だろうか。クリティカルパスは少しは増えるであろうが、元々の面積が小さい ので、目立った差は見られないだろう。

結論。面積が大きいものは、ムリに展開すると、逆にクリティカルパスが増えてしまう。なので、大きい面積のものは展開しないほうがよい。

#### 2-1):

制約なしで合成し、4 ビット、8 ビット、16 ビット ALU のビット幅と回路面積、およびビット幅と回路速度の関係を調べよ。

## 4ビット制約なし

## 8ビット制約なし

Total cell area: 407.000000

Total area: undefined

| Point                                      | Incr | Path    |

|--------------------------------------------|------|---------|

| input external delay                       | 0.00 | 0.00 r  |

| Sel[1] (in)                                | 0.00 | 0.00 r  |

| U250/Z (IV)                                | 0.44 | 0.44 f  |

| U249/Z (NR2)                               | 1.52 | 1.97 r  |

| U248/Z (ND2)                               | 0.35 | 2.32 f  |

| U223/Z (ND2)                               | 3.24 | 5.55 r  |

| r25/ADD_SUB (ALU_DW01_addsub_0)            | 0.00 | 5.55 r  |

| r25/U38/Z (EO)                             | 1.37 | 6.92 f  |

| r25/U34/Z (OR2)                            | 0.93 | 7.86 f  |

| r25/U33/Z (AO2)                            | 1.80 | 9.66 r  |

| r25/U32/Z (EN)                             | 1.22 | 10.87 f |

| r25/U31/Z (EN)                             | 1.80 | 12.68 r |

| r25/SUM[1] (ALU_DW01_addsub_0)             | 0.00 | 12.68 r |

| sub_0_root_add_40/A[1] (ALU_DW01_sub_0)    | 0.00 | 12.68 r |

| sub_0_root_add_40/U23/Z (NR2)              | 0.33 | 13.01 f |

| sub_0_root_add_40/U22/Z (EON1)             | 2.06 | 15.07 r |

| sub_0_root_add_40/U19/Z (NR2)              | 0.33 | 15.40 f |

| sub_0_root_add_40/U18/Z (EON1)             | 2.06 | 17.47 r |

| sub_0_root_add_40/U15/Z (NR2)              | 0.33 |         |

| sub 0 root add 40/U14/Z (EON1)             | 2.06 | 19.86 r |

| sub_0_root_add_40/U11/Z (NR2)              | 0.33 | 20.20 f |

| sub_0_root_add_40/U10/Z (EON1)             | 2.06 | 22.26 r |

| sub_0_root_add_40/U8/Z (NR2)               | 0.33 | 22.59 f |

| sub_0_root_add_40/U7/Z (EON1)              | 1.80 | 24.39 r |

| sub_0_root_add_40/U4/Z (NR2)               | 0.33 | 24.73 f |

| sub_0_root_add_40/U3/Z (EO1)               | 1.09 | 25.81 f |

| sub_0_root_add_40/U1/Z (EO)                | 1.23 | 27.05 f |

| sub_0_root_add_40/DIFF[7] (ALU_DW01_sub_0) | 0.00 | 27.05 f |

| U132/Z (MUX31L)                            | 1.58 | 28.63 r |

| U141/Z (IVI)                               | 0.12 | 28.75 f |

| U149/Z (ND2)                               | 0.69 | 29.44 r |

| U146/Z (AO3)                               | 0.68 | 30.13 f |

| U145/Z (AO2)                               | 1.18 | 31.31 r |

| U144/Z (AO7)                               | 0.40 | 31.71 f |

| Y[6] (out)                                 | 0.00 | 31.71 f |

| data arrival time                          |      | 31.71   |

## 16 ビット制約なし

Total cell area: 792.000000

Total area: undefined

| Point                                                          | Incr                 |                                          |

|----------------------------------------------------------------|----------------------|------------------------------------------|

| input external delay                                           | 0.00                 | 0.00 r                                   |

| Sel[1] (in)                                                    | 0.00                 | 0.00 r                                   |

| U449/Z (IV)                                                    | 0.37                 | 0.37 f                                   |

| U448/Z (NR2)                                                   | 1.52                 | 1.90 r                                   |

| U447/Z (ND2)                                                   | 0.35                 | 2.25 f                                   |

| U406/Z (ND2)                                                   | 5.65                 | 7.89 r                                   |

| r25/ADD_SUB (ALU_DW01_addsub_0)                                | 0.00                 | 7.89 r                                   |

| r25/U79/Z (EO)                                                 | 1.37                 | 9.26 f                                   |

| r25/U75/Z (OR2)<br>r25/U74/Z (AO2)                             | 0.93<br>1.80         | 10.19 f<br>12.00 r                       |

| r25/U18/Z (EN)                                                 | 1.22                 | 13.21 f                                  |

| r25/U17/Z (EN)                                                 |                      | 15.02 r                                  |

| r25/SUM[1] (ALU DW01 addsub 0)                                 | 1.80<br>0.00         | 15.02 r                                  |

| sub_0_root_add_40/A[1] (ALU_DW01_sub_0)                        | 0.00                 | 15.02 r                                  |

| sub 0 root add 40/U62/Z (NR2)                                  | 0.33                 | 15.35 f                                  |

| sub_0_root_add_40/U61/Z (EON1)                                 | 2.06                 | 17.41 r                                  |

| sub_0_root_add_40/U60/Z (NR2)                                  | 0.33                 | 17.74 f                                  |

| sub_0_root_add_40/U59/Z (EON1)                                 | 2.06                 | 19.81 r                                  |

| sub_0_root_add_40/U58/Z (NR2)                                  | 0.33                 | 20.14 f                                  |

| sub_0_root_add_40/U57/Z (EON1)                                 | 2.06<br>0.33         | 22.20 r                                  |

| sub_0_root_add_40/U56/Z (NR2)                                  |                      | 22.53 f                                  |

| sub_0_root_add_40/U55/Z (EON1)                                 | 2.06                 | 24.60 r                                  |

| sub_0_root_add_40/U54/Z (NR2)                                  | 0.33                 | 24.93 f                                  |

| sub_0_root_add_40/U54/Z (NR2)                                  | 0.33                 |                                          |

| sub_0_root_add_40/U53/Z (EO1)                                  | 1.29<br>0.84         | 26.22 f                                  |

| sub_0_root_add_40/U51/Z (AN2)                                  | 0.84                 | 27.06 f                                  |

| sub_0_root_add_40/U50/Z (AO4)                                  | 1.90                 |                                          |

| sub_0_root_add_40/U49/Z (NR2)                                  | 0.33<br>1.29<br>0.84 | 29.29 f                                  |

| sub_0_root_add_40/U48/Z (EO1)                                  | 1.29                 | 30.58 f                                  |

| sub_0_root_add_40/U46/Z (AN2)<br>sub 0 root add 40/U45/Z (AO4) | 1.90                 |                                          |

| sub 0 root add 40/044/Z (NR2)                                  |                      |                                          |

| sub 0 root add 40/U43/Z (EO1)                                  | 0.33<br>1.29         | 34.94 f                                  |

| sub 0 root add 40/U39/Z (AN2)                                  | 0.84                 |                                          |

| sub 0 root add 40/U38/Z (AO4)                                  |                      |                                          |

| sub 0 root add 40/U35/Z (NR2)                                  | 0.33                 | 38.02 f                                  |

| sub 0 root add 40/U34/Z (EO1)                                  | 1.90<br>0.33<br>1.29 | 39.30 f                                  |

| sub 0 root add 40/U30/Z (AN2)                                  | 0.84                 | 40.15 f                                  |

| sub 0 root add 40/U29/Z (AO4)                                  | 1.90                 |                                          |

| sub 0 root add 40/U26/Z (NR2)                                  | 0.33                 | 42.38 f                                  |

| sub 0 root add 40/U25/Z (EON1)                                 | 1.80                 | 44.18 r                                  |

| sub_0_root_add_40/U22/Z (NR2)                                  | 0.33                 | 44.52 f                                  |

| sub_0_root_add_40/U21/Z (EO1)                                  | 1.09                 | 45.60 f                                  |

| sub_0_root_add_40/U21/Z (EO1)                                  | 1.09                 | 45.60 f                                  |

| sub_0_root_add_40/U19/Z (EO)                                   | 1.23                 | 46.83 f                                  |

| sub_0_root_add_40/DIFF[15] (ALU_DW01_sub_0)                    | 0.00                 | 46.83 f                                  |

| U234/Z (MUX31L)                                                | 1.58                 | 48.42 r                                  |

| U253/Z (IVI)                                                   | 0.12<br>0.69         | 48.54 f                                  |

| U327/Z (ND2)                                                   | 0.69                 | 49.23 r                                  |

| U324/Z (AO3)                                                   | 0.68                 | 49.91 f<br>51.10 r<br>51.50 f<br>51.50 f |

| U323/Z (AO2)                                                   | 1.18                 | 51.1U r                                  |

| U322/Z (AO7)                                                   | 0.40                 | 51.5U f                                  |

|                                                                | 0.00                 | 31.5U T                                  |

| Y[14] (out) data arrival time                                  |                      | 51.50                                    |

## 結論:

ビット幅が大きくなれば面積、クリティカルパス共に増加する。

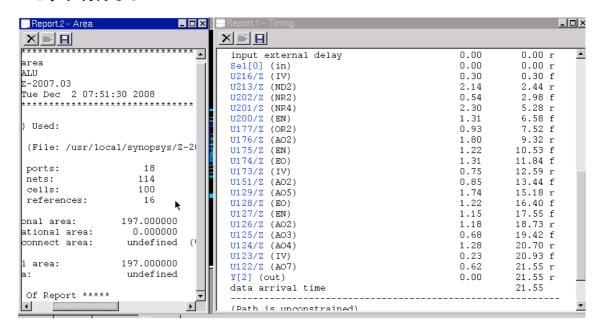

## 2-2):

最小速度で合成し、4 ビット、8 ビット、16 ビット ALU のビット幅と回路面積、およびビット幅と回路速度の関係を調べよ。

## 4ビット制約あり

Number of ports: 18

Number of nets: 185

Number of cells: 170

Number of references: 27

Combinational area: 318.000000

Noncombinational area: 0.000000

Net Interconnect area: undefined (Wire load has zero n

Total cell area: 318.000000

Total area: undefined

| Point                                                                                                                                                                                                                                                                                                            | Incr                                                                                                                                                                 | Path                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| input external delay Sel[0] (in) U200/Z (B4IP) U216/Z (ND2I) U289/Z (NR2I) U224/Z (NR3P) U282/Z (ENI) U132/Z (IVI) U187/Z (ND2I) U275/Z (ND2I) U274/Z (ND2I) U274/Z (ND2I) U234/Z (ENI) U138/Z (ND2I) U234/Z (ENI) U138/Z (ND2I) U250/Z (AO2P) U251/Z (AO5P) U261/Z (ENI) U277/Z (ENI) U277/Z (ENI) U277/Z (ENI) | 0.00<br>0.00<br>0.04<br>0.25<br>0.24<br>1.09<br>0.53<br>0.24<br>0.12<br>0.12<br>0.48<br>0.48<br>0.48<br>0.48<br>0.48<br>0.49<br>0.57<br>1.24<br>0.42<br>0.42<br>0.30 | 0.00 r<br>0.00 r<br>0.04 f<br>0.29 r<br>0.53 f<br>1.62 r<br>2.15 f<br>2.39 r<br>2.51 f<br>2.77 r<br>2.89 f<br>3.36 f<br>4.13 r<br>4.71 f<br>5.94 r<br>6.37 f<br>6.79 f<br>7.09 r |

| U122/Z (AN2I)<br>U273/Z (AO3P)                                                                                                                                                                                                                                                                                   | 0.39 <b>\</b><br>0.50                                                                                                                                                | 7.47 r<br>7.97 f                                                                                                                                                                 |

| U178/Z (IVI) U124/Z (ND2I) U125/Z (AN2I) U264/Z (ND2I) Y[2] (out) data arrival time                                                                                                                                                                                                                              | 0.24<br>0.12<br>0.61<br>0.21<br>0.00                                                                                                                                 | 8.21 r<br>8.33 f<br>8.94 f<br>9.15 r<br>9.15 r<br>9.15                                                                                                                           |

## 8ビット制約あり

Total cell area: 664.000000

Total area: undefined

| Point                                      | Incr         | Path             |

|--------------------------------------------|--------------|------------------|

| input external delay                       | 0.00         | 0.00 r           |

| Sel[1] (in)                                | 0.00         | 0.00 r           |

| U130/Z (B4IP)                              | 0.04         | 0.04 f           |

| U129/Z (NR2I)                              | 0.57         | 0.61 r           |

| U128/Z (ND2I)                              | 0.12         | 0.73 f           |

| U184/Z (ND2I)                              | 0.25         | 0.98 r           |

| U187/Z (IVI)                               | 0.17         | 1.16 f           |

| U300/Z (AO3P)                              | 0.68         | 1.84 r           |

| r25/B[0] (ALU_DW01_addsub_1)               | 0.00         | 1.84 r           |

| r25/U122/Z (ENI)                           | 0.58         | 2.42 f           |

| r25/U105/Z (NR2I)                          | 0.57<br>0.26 | 2.99 r<br>3.26 f |

| r25/U104/z (ND2I)<br>r25/U103/z (IVI)      | 0.29         | 3.55 r           |

| r25/U38/Z (NR2I)                           | 0.29         | 3.76 f           |

| r25/U100/Z (ND2I)                          | 0.30         | 4.05 r           |

| r25/U94/Z (ENI)                            | 0.62         | 4.67 r           |

| r25/SUM[2] (ALU DW01 addsub 1)             | 0.00         | 4.67 r           |

| sub_0_root_add_40/A[2] (ALU_DW01_sub_0)    | 0.00         | 4.67 r           |

| sub 0 root add 40/U14/Z (ND2I)             | 0.12         | 4.79 f           |

| sub 0 root add 40/U15/Z (IVI)              | 0.24         | 5.03 r           |

| sub_0_root_add_40/U69/Z (ND2I)             | 0.12         | 5.15 f           |

| sub 0 root add 40/U68/Z (AN2I)             | 0.64         | 5.79 f           |

| sub 0 root add 40/U63/Z (ND2I)             | 0.25         | 6.04 r           |

| sub_0_root_add_40/U51/Z (ND2I)             | 0.12         | 6.16 f           |

| sub_0_root_add_40/U50/Z (ND2I)             | 0.25         | 6.41 r           |

| sub 0 root add 40/U49/Z (ENI)              | 0.48         | 6.89 f           |

| sub 0 root add 40/DIFF[5] (ALU DW01 sub 0) | 0.00         | 6.89 f           |

| U298/Z (MUX31LP)                           | 1.25         | 8.14 r           |

| U139/Z (IVI)                               | 0.18         | 8.32 f           |

| U306/Z (ND2I)                              | 0.29         | 8.61 r           |

| U305/Z (AO3P)                              | 0.50         | 9.11 f           |

| U270/Z (ND2I)                              | 0.25         | 9.36 r           |

| U272/Z (AN2I)                              | 0.39         | 9.75 r           |

| U273/Z (AO7P)                              | 0.28         | 10.03 f          |

| Ψ[4] (out)                                 | 0.00         | 10.03 f          |

| data arrival time                          |              | 10.03            |

## 16 ビット制約あり

Total cell area: 1062.000000

Total area: undefined

| Point                                                                                                                                                                                                                                                                                                                                                                                                                   | Incr                                                                                                                                         | Path                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| input external delay Sel[1] (in) U398/Z (B4IP) U463/Z (NR2I) U443/Z (ND2I) U255/Z (IVI) U257/Z (IVI) U257/Z (IVI) U471/Z (A07P) r25/B[1] (ALU_DW01_addsub_0) r25/U129/Z (ENI) r25/U129/Z (ND2I) r25/U121/Z (ND2I) r25/U121/Z (ND2I) r25/U117/Z (ND2I) r25/U117/Z (ND2I) r25/U113/Z (ND2I) r25/U113/Z (ND2I) r25/U113/Z (ND2I) r25/U113/Z (ND2I) r25/U111/Z (ND2I) r25/U111/Z (ND2I) r25/U111/Z (ND2I) r25/U110/Z (ND2I) | 0.00<br>0.00<br>0.04<br>0.57<br>0.34<br>0.24<br>0.17<br>0.68<br>0.00<br>0.48<br>0.30<br>0.12<br>0.30<br>0.12<br>0.30<br>0.12<br>0.30<br>0.12 | 0.00 r<br>0.00 r<br>0.04 f<br>0.61 r<br>0.95 f<br>1.19 r<br>1.37 f<br>2.05 r<br>2.53 f<br>2.82 r<br>2.94 f<br>3.24 r<br>3.36 f<br>3.66 r<br>3.78 f<br>4.08 r<br>4.50 r |

| r25/U107/Z (ND2I) r25/U106/Z (ND2I) r25/U103/Z (ND2I) r25/U102/Z (ND2I) r25/U99/Z (ND2I) r25/U99/Z (ND2I) r25/U98/Z (ND2I) r25/U97/Z (ND2I) r25/U97/Z (ND2I) r25/U96/Z (ND2I) r25/U96/Z (ND2I) r25/U94/Z (ND2I) r25/U94/Z (ND2I) r25/U94/Z (ND2I) r25/U86/Z (ND2I) r25/U86/Z (ND2I) r25/U87/Z (ND2I) r25/U77/Z (ND2I) r25/U77/Z (ND2I) r25/U76/Z (ND2I)                                                                 | 0.12<br>0.30<br>0.20<br>0.25<br>0.20<br>0.25<br>0.12<br>0.30<br>0.12<br>0.30<br>0.12<br>0.30<br>0.12                                         | 4.62 f<br>4.91 r<br>5.11 f<br>5.36 r<br>5.56 f<br>5.82 r<br>5.94 f<br>6.23 r<br>6.35 f<br>6.65 r<br>6.77 f<br>7.07 r<br>7.27 f<br>7.52 r                               |

| r25/U76/2 (ND21) r25/U68/2 (ND21) r25/U67/2 (ND21) r25/U59/2 (ND21) r25/U18/2 (ND21) r25/U52/2 (ENI) r25/SUM[14] (ALU_DW01_addsub_0) sub_0_root_add_40/A[14] (ALU_DW01_sub_1)                                                                                                                                                                                                                                           | 0.25<br>0.12<br>0.30<br>0.20<br>0.25<br>0.58<br>0.00                                                                                         | 7.52 r<br>7.64 f<br>7.94 r<br>8.14 f<br>8.39 r<br>8.97 f<br>8.97 f                                                                                                     |

```

0.29

9.27 r

sub_0_root_add_40/U87/Z (IVI)

sub_0_root_add_40/U24/Z (ND2I)

0.12

9.39 f

sub_0_root_add_40/U72/Z (ND2I)

0.25

9.64 r

0.12

9.76 f

sub_0_root_add_40/U12/Z (ND2I)

sub_0_root_add_40/U13/Z (IVI)

0.24

10.00 r

sub_0_root_add_40/U69/Z (ND2I)

0.12

10.12 f

sub_0_root_add_40/U68/Z (ENI)

0.48

10.60 f

sub_0_root_add_40/DIFF[15] (ALU_DW01_sub_1)

0.00

10.60 f

U497/Z (MUX31LP)

1.25

11.85 r

0.12

11.97 f

U253/Z (IVI)

U498/Z (ND2I)

0.33

12.31 r

U228/Z (A03P)

0.50

12.80 f

U481/Z (ND2I)

0.25

13.06 r

U483/Z (AN2I)

0.34

13.40 r

0.06

13.45 f

U459/Z (ND2I)

¥[14] (out)

0.00

13.45 f

13.45

data arrival time

```

#### 結論:

ビット幅が大きくなれば面積、クリティカルパス共に増加する。

#### まとめ:

制約(クリティカルパスの最速化)を指定すると、その制約を第一と考え、その制約に対応するもの以外はあまり重要視されない。今回の実験では、クリティカルパスが 4,8,16 ビットそれぞれが短縮されたが、面積が増えていた。(面積よりもクリティカルパスが重要視されている)