4.1多ビット加算器 P63

琉球大学情報工学科 和田 知久

- 教科書のリスト4.3にコンポネーントを用いた4ビット加算器のVHDL記述がある。

- 今回はもっと簡単な算術演算子を用いた記述を学習する。

- リスト4.3ではAND,XORなどの論理演算(論理素子)を用いたVHDL記述でHAを設計し、それを多数接続して4ビット加算器を実現している。

- リスト4.4では加算という算術演算を用いることで簡単に記述できている。

- design_analyzerで回路合成すると、この”+”加算演算は自動的に論理演算に変換される。

算術演算子を用いた4ビット加算器のVHDL記述 (演習4.3、リスト4.4)

リスト4.4(コピー)

もう少し細かく見ると

|

ライブラリ宣言 |

library IEEE; |

ライブラリ宣言、STD_LOGICを使用する場合に必要 IEEE.std_logic_unsignedは、std_logic_vector型で |

|

ENTITY宣言 |

entity ADDER4 is |

エンティティ宣言 |

|

port ( A, B : in std_logic_vector(3

downto 0); |

ポート宣言(入出力信号と信号のデータタイプを定義) |

|

|

end ADDER4; |

エンティティ終了。";"忘れるな! |

|

|

回路の中味の記述 |

architecture BEHAVIOR of ADDER4 is |

アーキテクチャ宣言 |

|

begin |

算術演算”+”を用いて加算を行う場合、左辺のビット長と |

テストベンチによる検証 P89

もう少し細かく見ると

|

ライブラリ宣言 |

library IEEE; |

conv_std_logic_vector関数を使うために、 |

|

エンティティ |

entity TESTBENCH_HA is |

エンティティ宣言 |

|

アーキテクチャ |

architecture SIM_DATA of TESTBENCH_HA is |

|

|

component ADDER4 |

以下の用いる回路部品(コンポーネント)の宣言 |

|

|

signal SA, SB : std_logic_vector(3

downto 0); |

新たに使用する信号の宣言 |

|

|

begin |

実際のテストベンチ回路 教科書P89 リスト4.17に同様の例がある。 |

|

|

-- configuration宣言(最上位階層では必須) |

VHDLではひとつのエンティティに複数のアーキテクチャを |

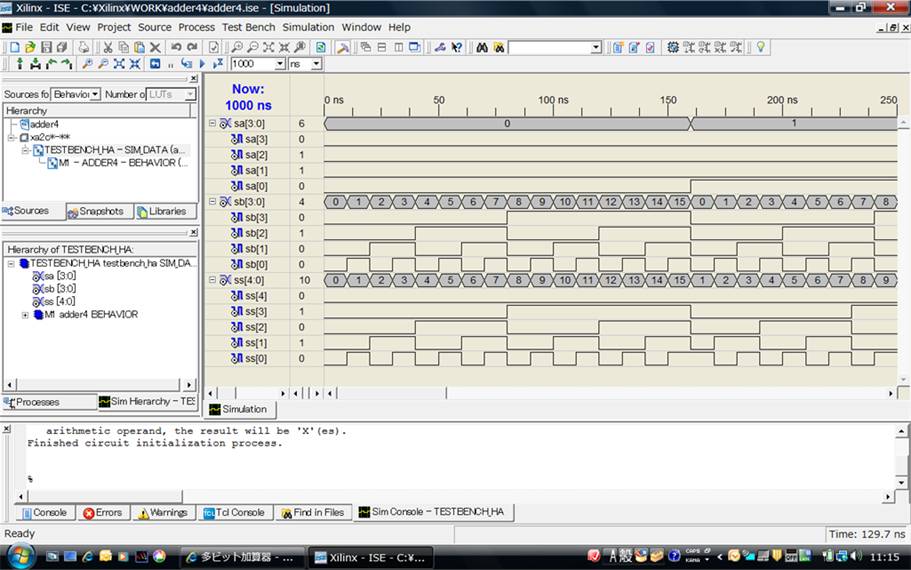

実習1. VHDL記述のシミュレーション

1) 上記2つのファイルを自分のPC上のディレクトリーにコピーして作業を始めよ。

adder4.vhd リスト4.4

adder4_test.vhd テストベンチ

2) ISEにてシミュレーションを実行し、動作を確認せよ!

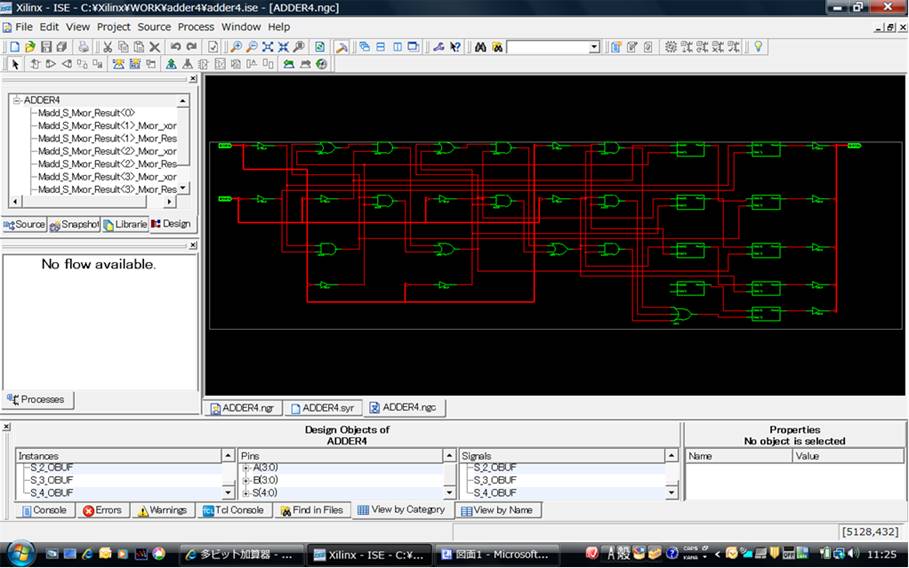

実習2. 回路を合成せよ

1) XSTにて回路を合成し、TECHNOLOGY SCHEMATICを確認せよ!

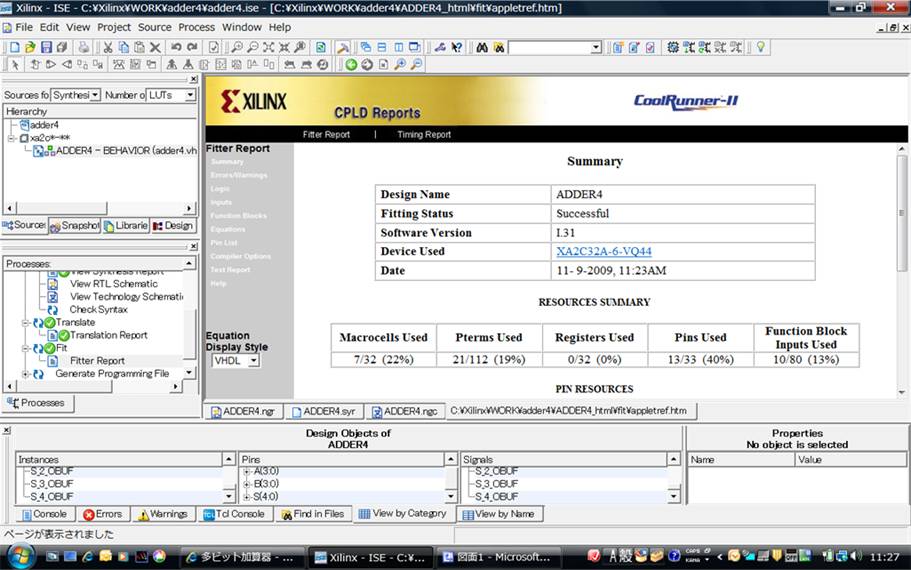

実習3. FPGA(CPLD)の利用率をしらべよ

1) Synthesisの後に、Translate、Fitを実行し、Fitter Reportを確認せよ

HW1 WEBCLASSに提出すること!

1)[オーバーフローのチェック]

上記実習の例では2つの4ビット入力を加算して5ビット出力を出力しているが、入出力すべて4ビットに改造し、

S <= ('0' & A) + ('0' & B);

の部分を

S <= A + B;

のように変更した場合、たとえばA=15、B=15ではSは4ビットでは表示できない値になる。実際にSが4ビット幅の場合Sの値はどうなるか?

上記改造前と後でFitter ReportのMacrocells Usedの変化をレポートせよ!

2)[ビット幅変更による回路の変化]

上記実習の例を8ビット入力+8ビット入力=9ビット出力になるように改造し、シミュレーションで動作確認を行い、回路合成を行え。

レポートには以下の内容を含むこと

- A=255、B=255の時のシミュレーション波形

- TECHNOLOGY SCHEMATIC図

- Fitter Report を示し、Macrocells Usedの変化をレポートせよ

以上