(1) ISEを使用して、

VHDLシミュレーションをする。

# 必要ファイルを以下よりダウンロード

## 吉田先生の教科書サポートページ

- [http://www.fts.ie.u-ryukyu.ac.jp/support/vhdl\\_digital/VHDL-src.html](http://www.fts.ie.u-ryukyu.ac.jp/support/vhdl_digital/VHDL-src.html)

- [3. HALF ADDER-std.vhd](#)

- [14. TESTBENCH HA.vhd](#)

**HDLソースファイル一覧**

本書に掲載されているVHDL記述、合成結果の回路図、シミュレーション波形をダウンロードできます。また参考用として、各VHDL記述に対応したVerilog-HDL記述も参照できます。

| No. | 回路名                | 掲載<br>ページ | リスト<br>番号 | VHDLファイル<br>(Verilog-HDLファイル(*1))    | 論理合成(*2)<br>シミュレーション(*3)         |

|-----|--------------------|-----------|-----------|--------------------------------------|----------------------------------|

| 1   | 半加算器(bit型使用)       | 24        | 2.1       | HALF_ADDER-bit.vhd<br>(HALF_ADDER.v) | <input type="button" value="○"/> |

| 2   | 全加算器のキャリー生成回路      | 47        | 3.1       | FA_CARRY.vhd<br>(FA_CARRY.v)         | <input type="button" value="○"/> |

| 3   | 半加算器(std_logic型使用) | 59        | 4.1       | HALF_ADDER-std.vhd<br>(HALF_ADDER.v) | <input type="button" value="○"/> |

| 4   | 全加算器(コンポーネント使用)    | 60        | 4.2       | FULL_ADDER.vhd<br>(FULL_ADDER.v)     | <input type="button" value="○"/> |

| 5   | 4ビット加算器(コンポーネント使用) | 62        | 4.3       | ADDER4-comp.vhd<br>(ADDER4-comp.v)   | <input type="button" value="○"/> |

| 6   | 4ビット加算器(算術演算子使用)   | 63        | 4.4       | ADDER4-op.vhd<br>(ADDER4-op.v)       | <input type="button" value="○"/> |

| 7   | 4ビットマルチプレクサ(セレクタ)  | 66        | 4.5       | MUX4.vhd<br>(MUX4.v)                 | <input type="button" value="○"/> |

| 8   | 4ビットデマルチプレクサ       | 68        | 4.6       | DEMUX4.vhd<br>(DEMUX4.v)             | <input type="button" value="○"/> |

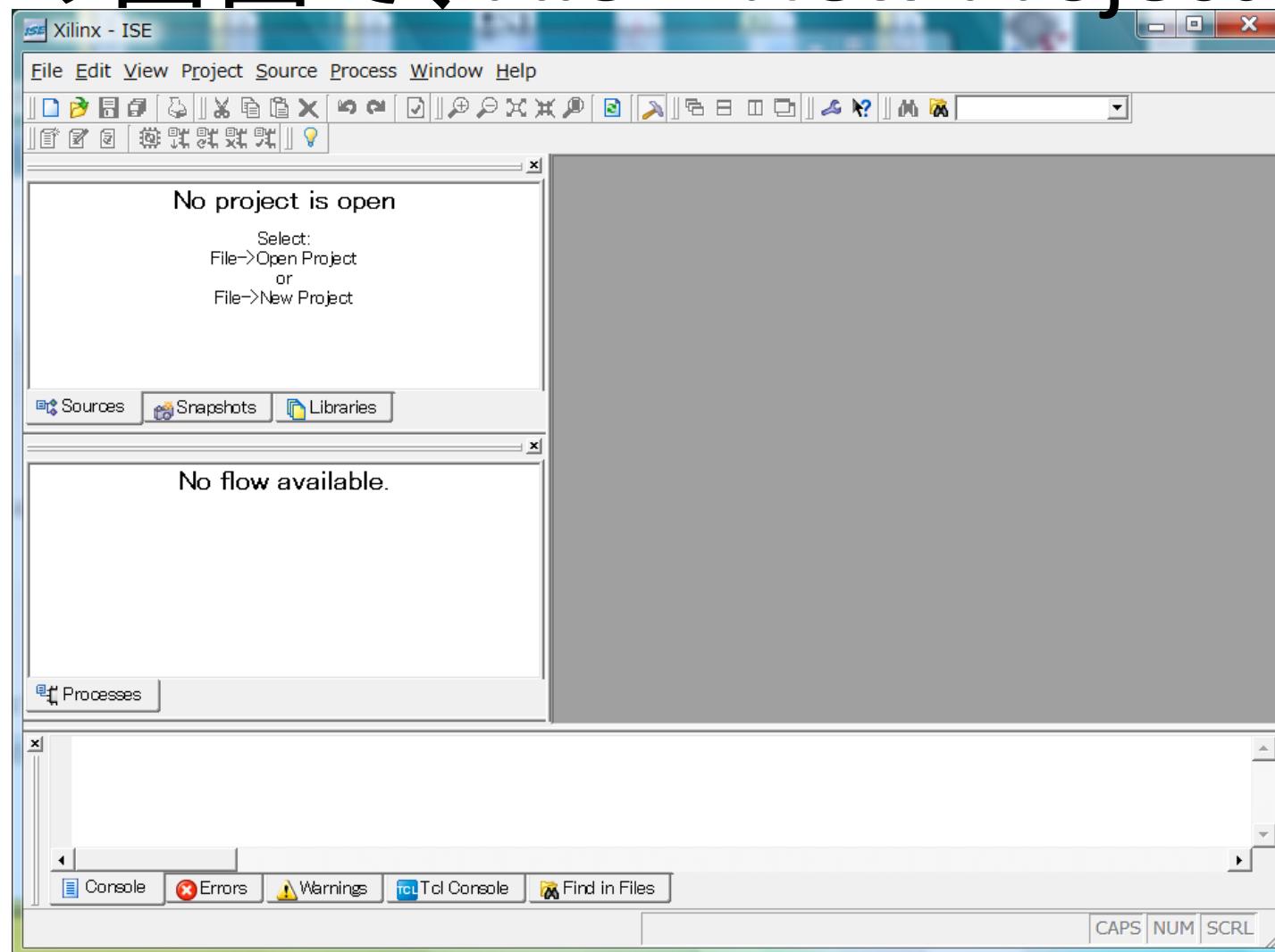

ISEを起動して

この画面で、File-> New Project

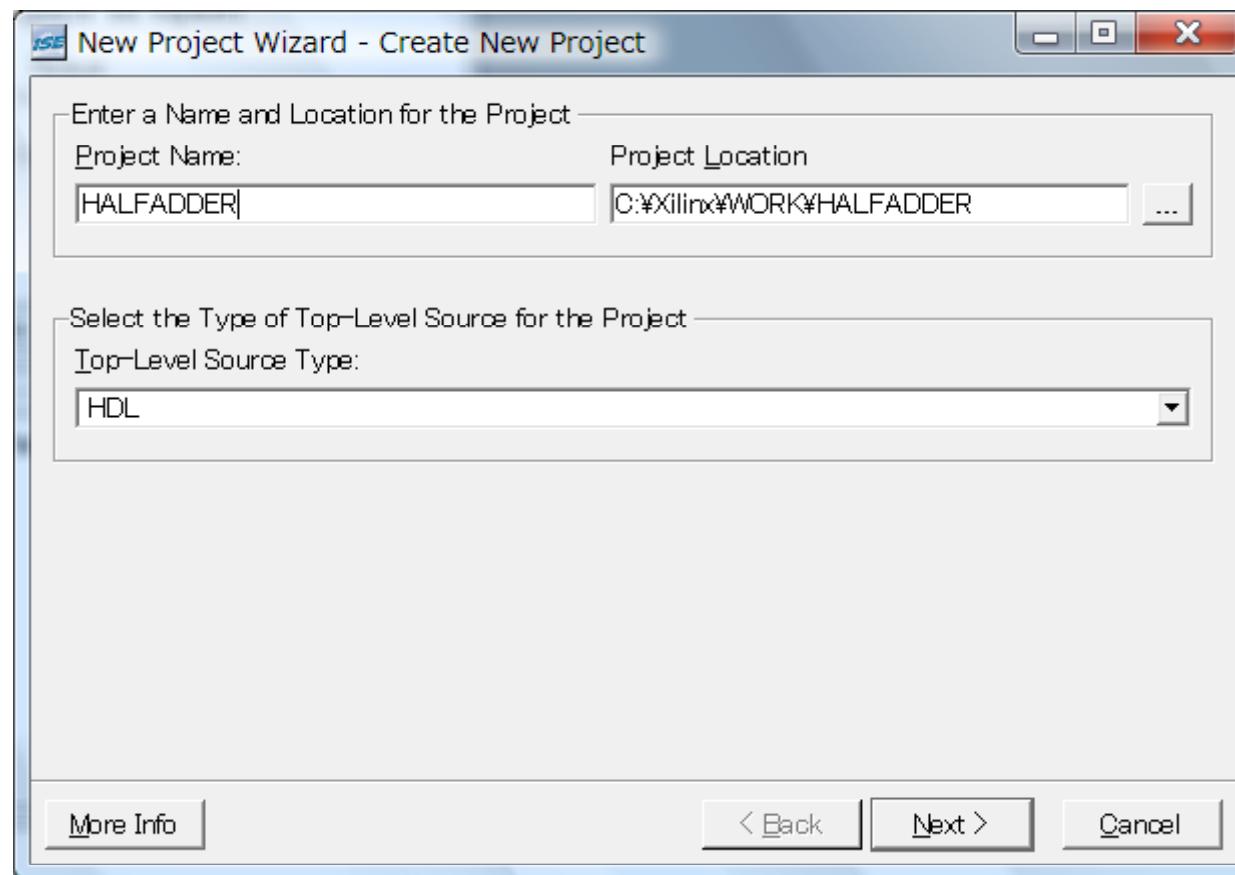

# お好みのディレクトリと プロジェクト名を設定

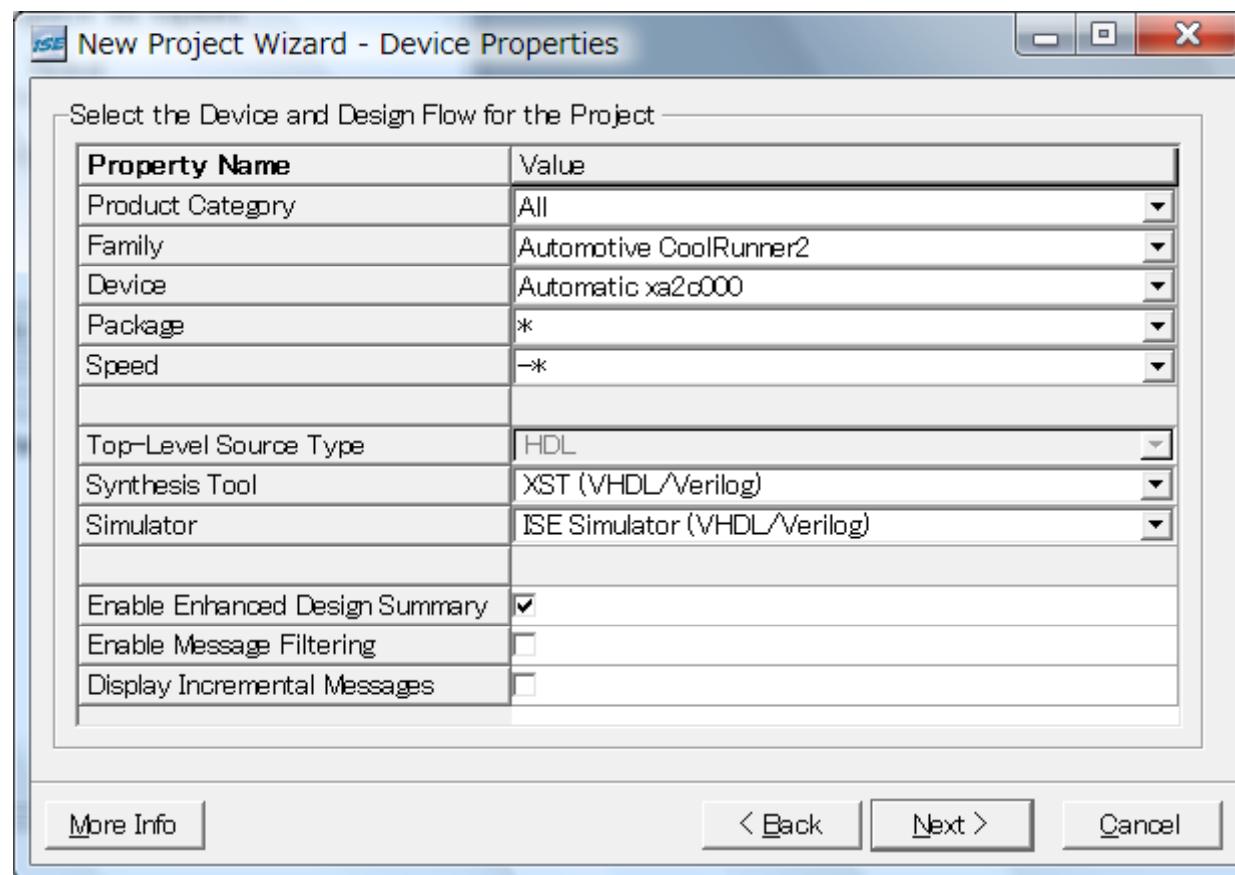

# ここは設定なし

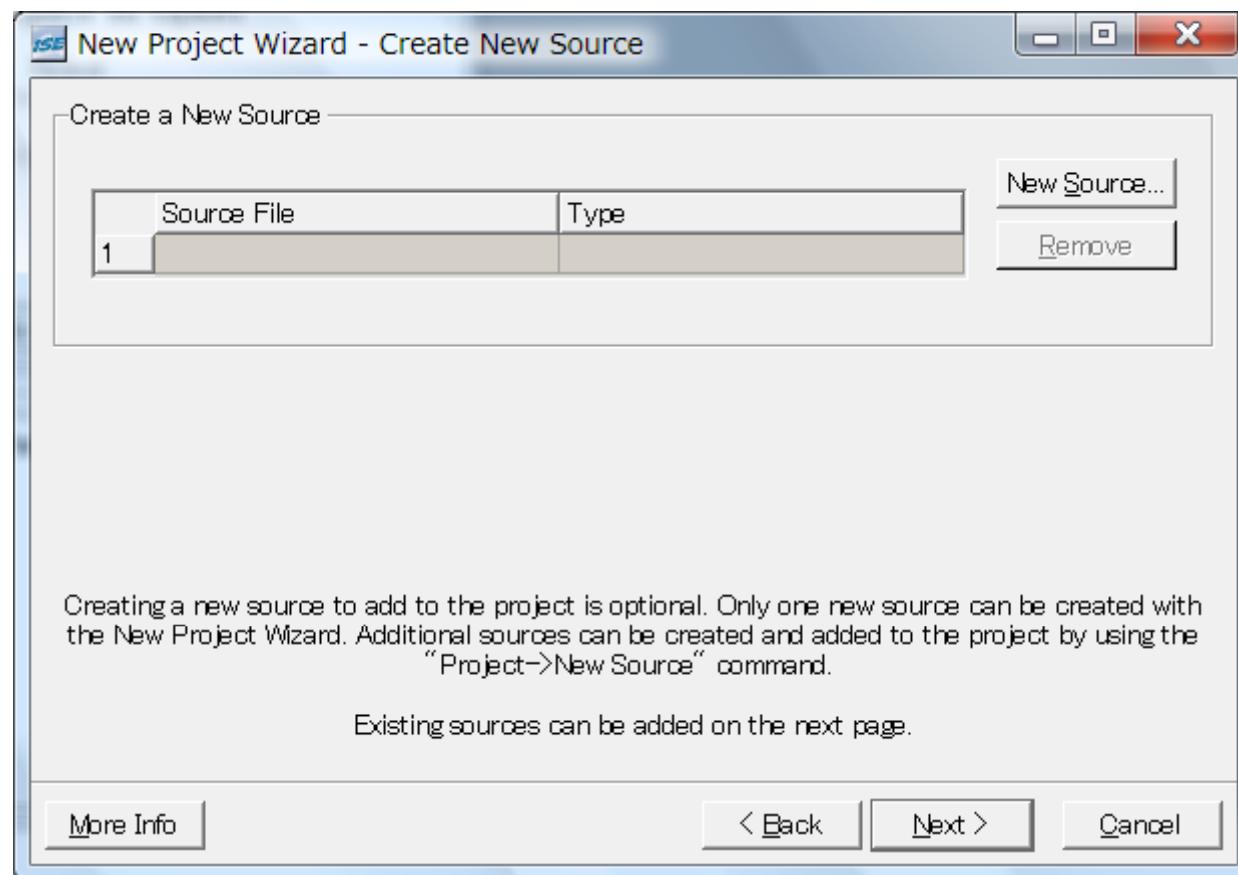

# ここも、設定なし

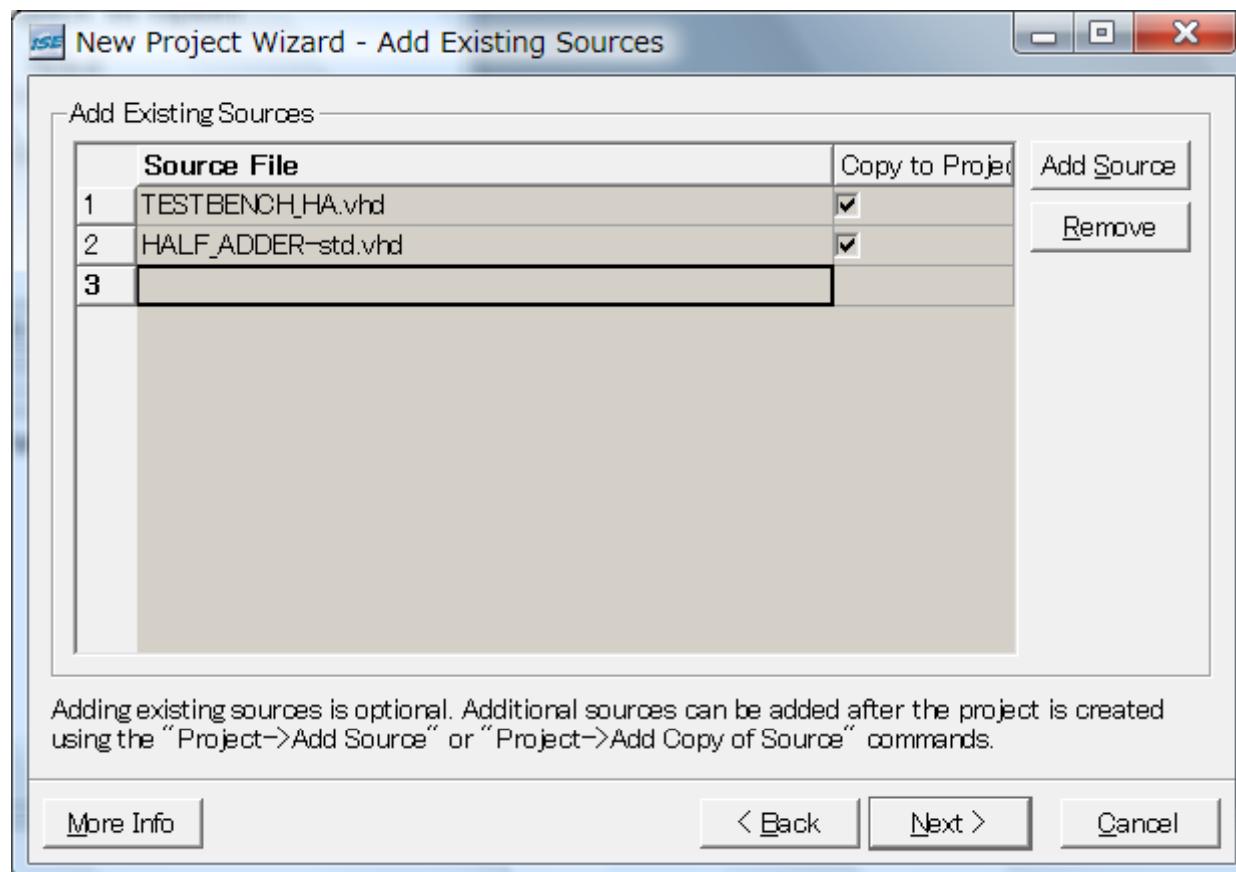

# Add\_Sourceで、シミュレーションファイルを追加

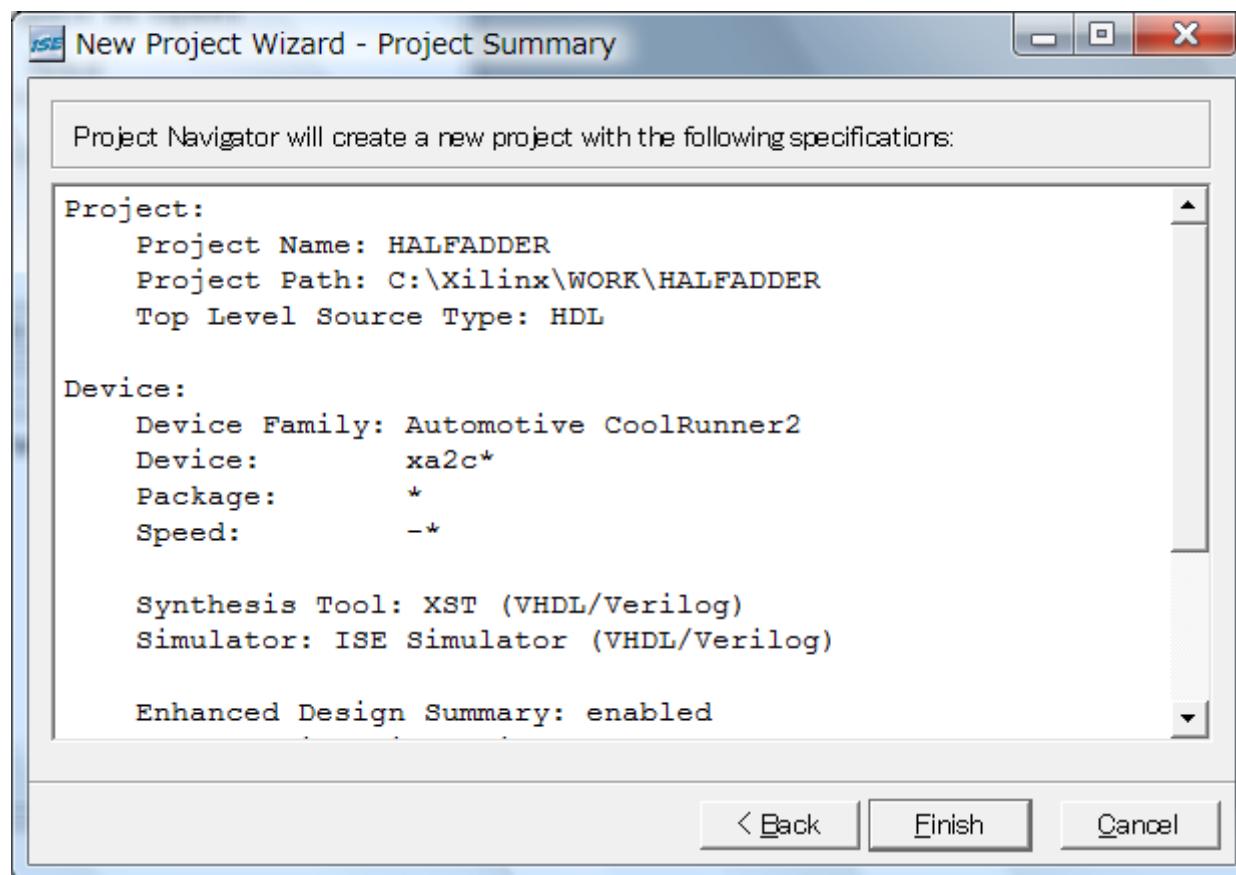

# 設定を確認し、Finish

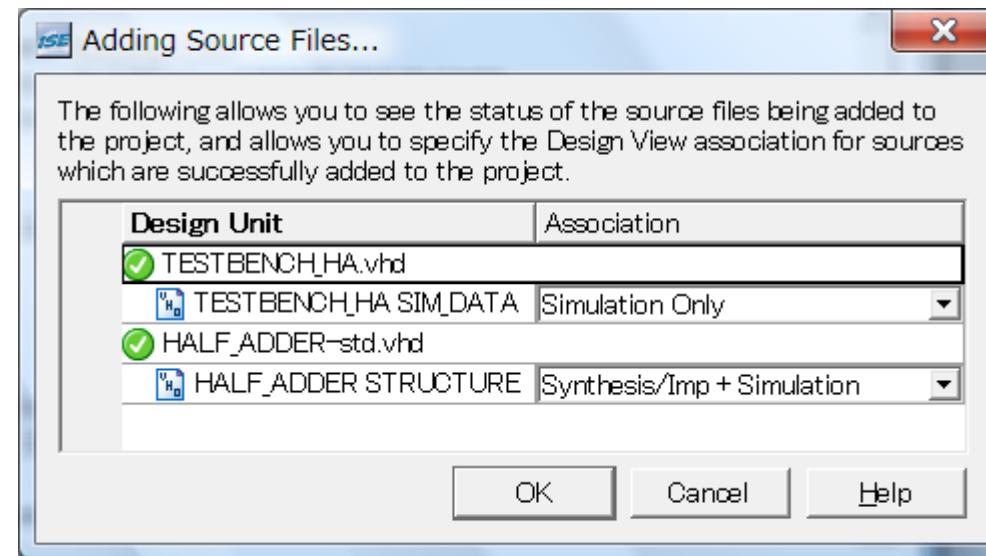

# 確認し、OK!

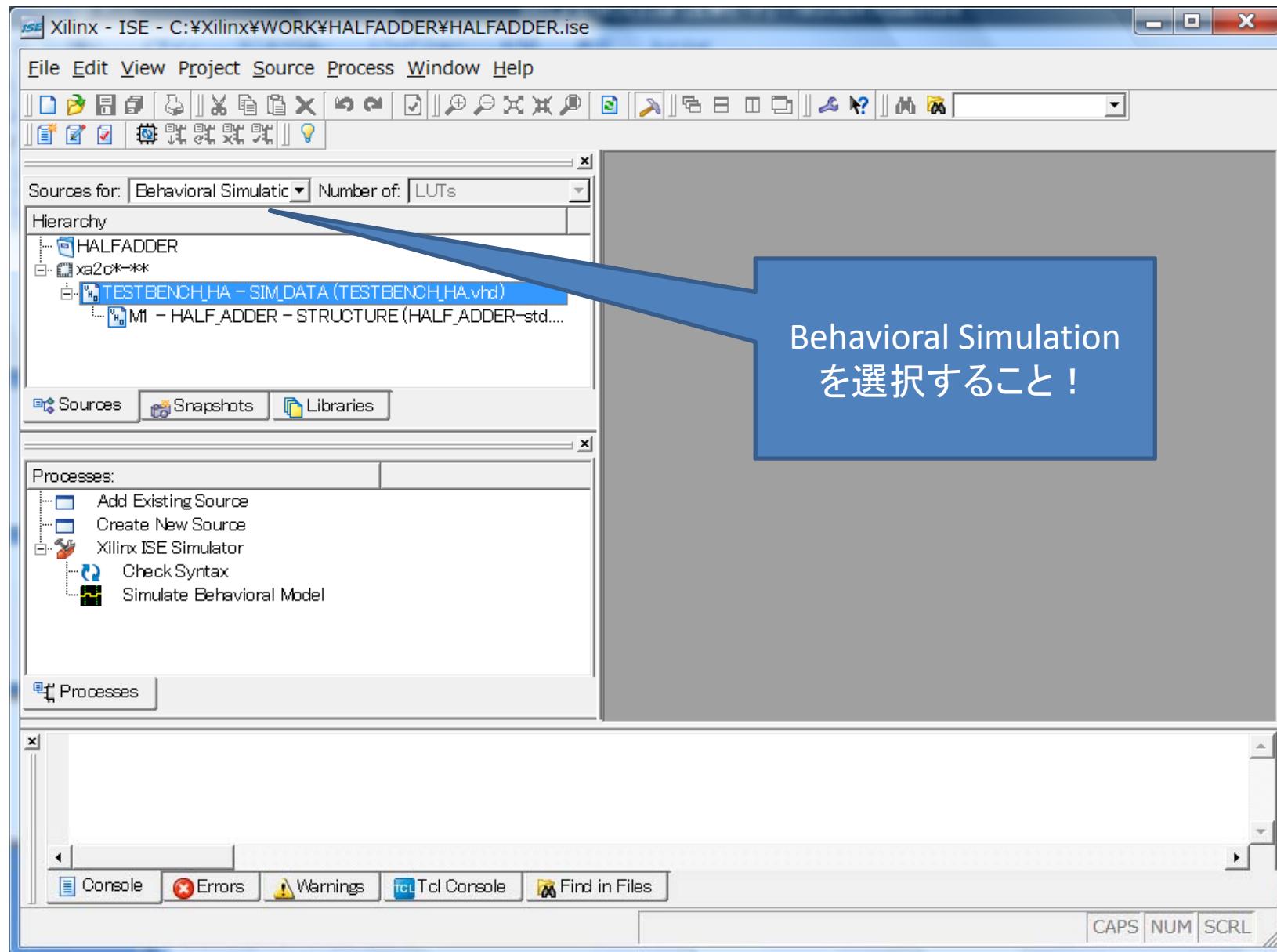

# このようになればOK！

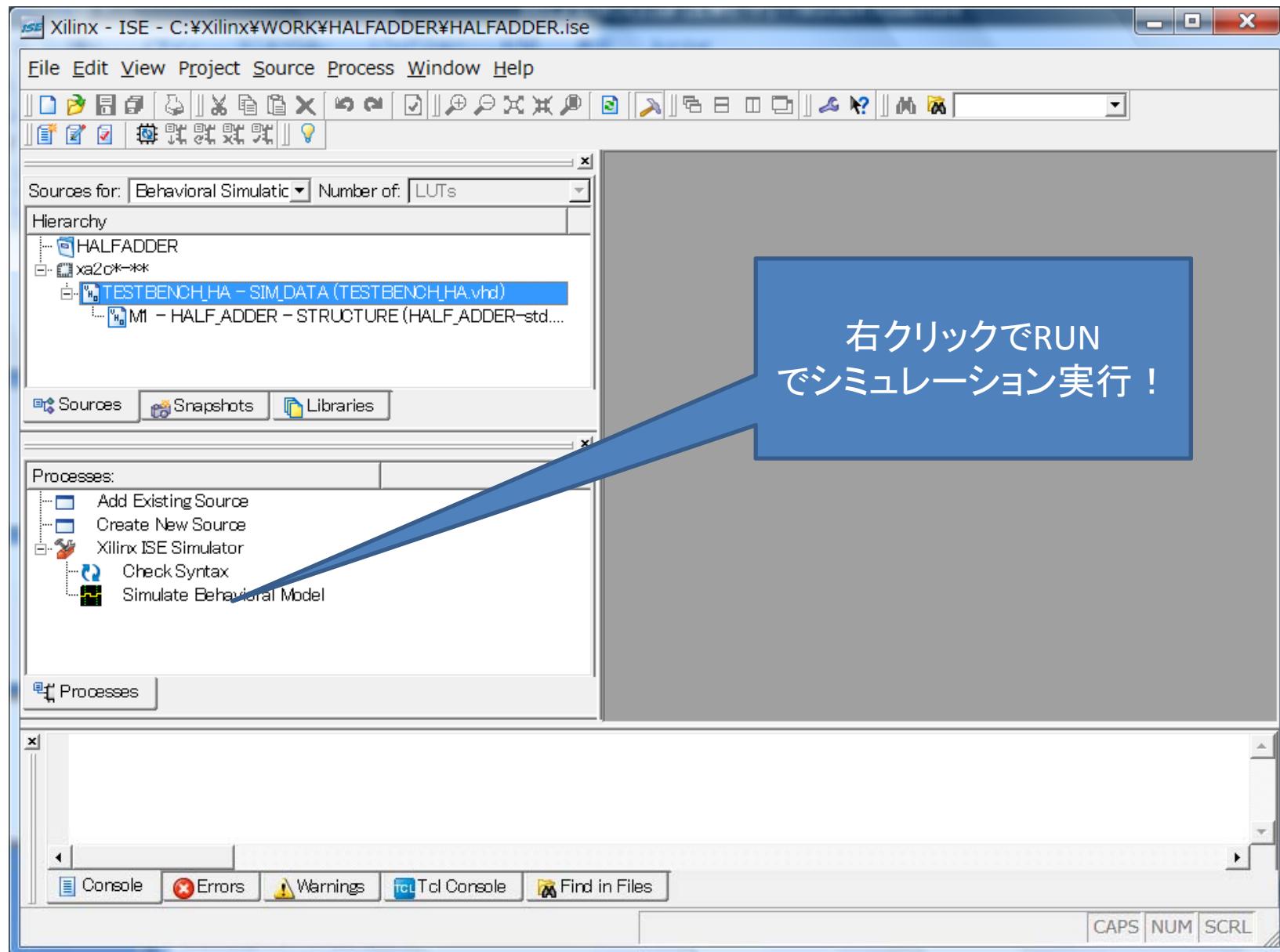

# シミュレーション実行方法

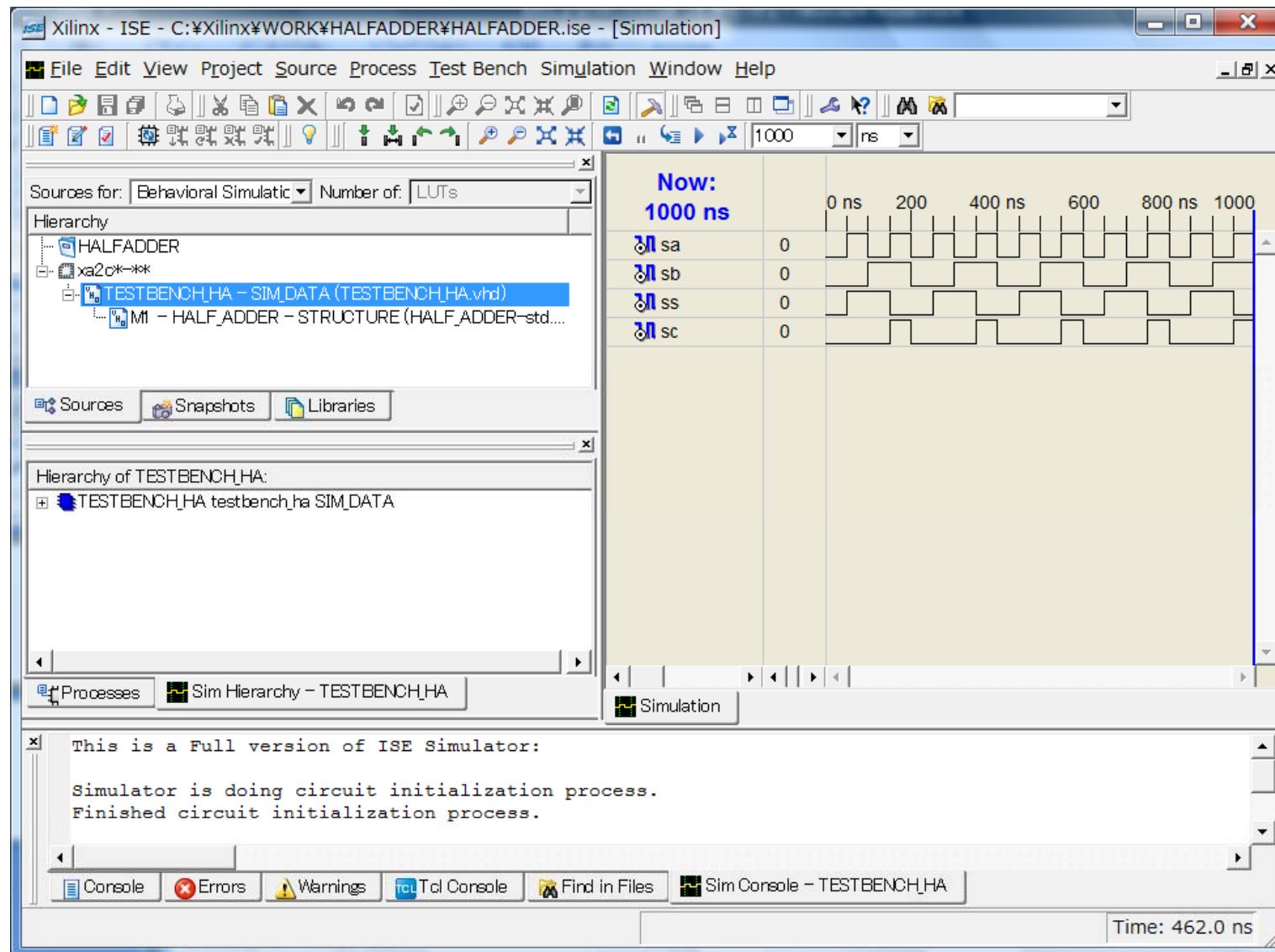

# シミュレーション実行され、動作波形が表示されます！

# アナウンス

- 次回 10/19はツール関連の指導をTAより実施予定

- TA: ファイヤー和田研M2 宮野智法

- [tomo@lsi.ie.u-ryukyu.ac.jp](mailto:tomo@lsi.ie.u-ryukyu.ac.jp)

- 10/26はオンラインテスト(1回目)で、本日のデモに類することを各自のコンピュータでやってもらう予定です。