H21年度前期 ディジタル回路 期末試験 2009/8/6

問題1-6:2枚、解答用紙1枚 教科書ノート持込化

解答用紙のみ回収、解答は解答用紙へ！

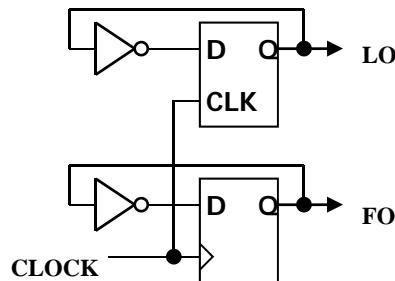

1. 以下のDラッチと、Dフリップフロップを含む回路の出力波形を示せ。NOT回路の遅延を1ns、ラッチ・フリップフロップの遅延を2nsとし、ラッチ・フリップフロップの初期値は“0”とする。(10点)

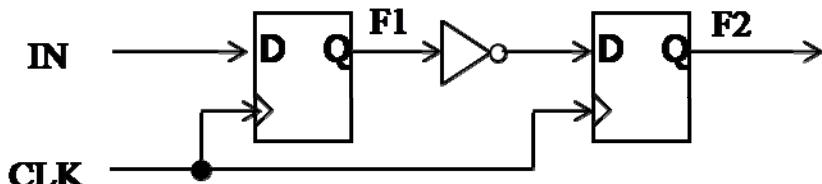

2. 以下の順序回路の状態遷移図を完成させよ。(10点)

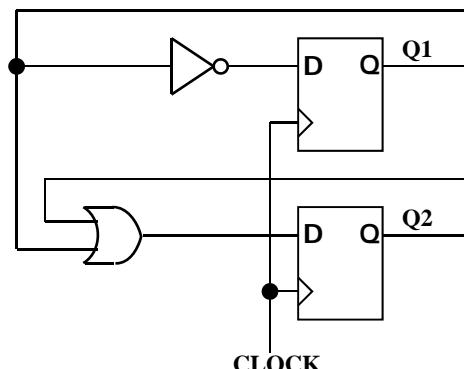

3. 以下の順序回路の動作波形図を完成させよ。但し、Q1、Q2の初期値を‘0’とする。(10点)

4. 以下のブール式で示される組み合わせ回路をNANDゲートとNOTゲートのみを用いて設計せよ。

また、組み合わせ回路の機能をなんというか？(6+4点)

$$Y = \overline{A} \cdot B + A \cdot \overline{B}$$

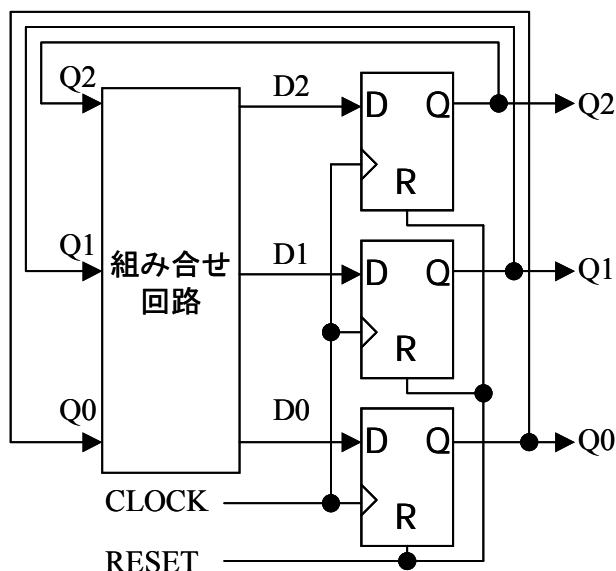

5. RESET付D-FFを用い以下の手順にしたがって、整数値で示して $0 \rightarrow 7 \rightarrow 1 \rightarrow 6 \rightarrow 2 \rightarrow 5 \rightarrow 3 \rightarrow 4 \rightarrow 0 \rightarrow 7 \rightarrow 1 \dots$ を繰り返すカウンターを設計せよ。(各9点X4=36点)

(i) Q2をMSB、Q0をLSBとして、以下のような回路構成にする。組み合せ回路のカルノー図を作成し、簡略化を行え(適切に○で囲め!)。

(ii) 簡略化された加法標準形のブール式を示せ。

(iii) (ii)の結果より、NOTとNANDだけを用いて、組み合せ回路を実現せよ!

(iv) その組み合せのトランジスタ数はいくつ?

| Q2 | Q1 | Q0 | D2 | D1 | D0 |

|----|----|----|----|----|----|

| 0  | 0  | 0  |    |    |    |

| 0  | 0  | 1  |    |    |    |

| 0  | 1  | 0  |    |    |    |

| 0  | 1  | 1  |    |    |    |

| 1  | 0  | 0  |    |    |    |

| 1  | 0  | 1  |    |    |    |

| 1  | 1  | 0  |    |    |    |

| 1  | 1  | 1  |    |    |    |

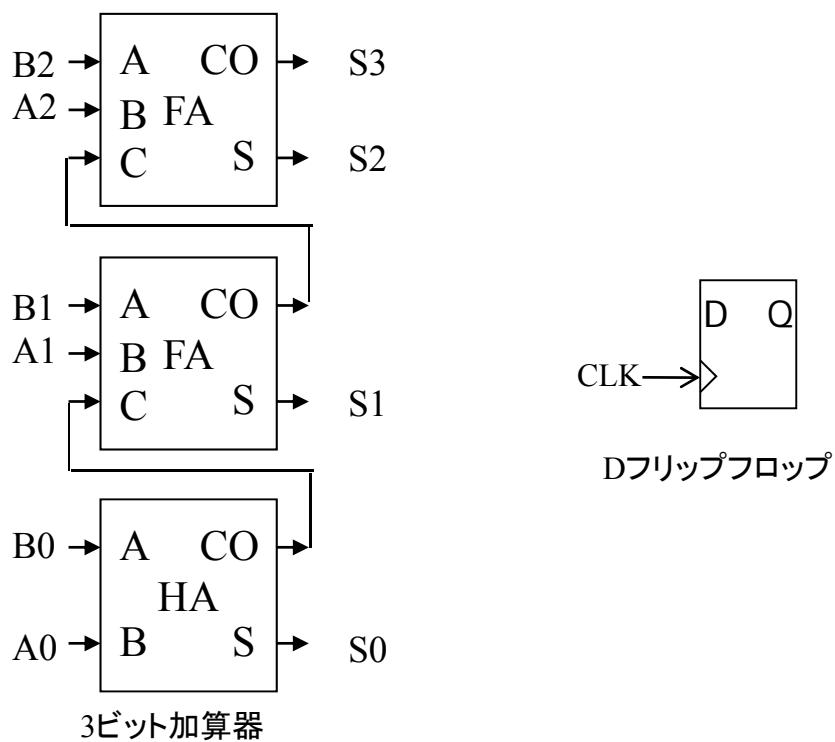

6. 以下の回路図は3ビットの数 $A=(A_2, A_1, A_0)$ と $B=(B_2, B_1, B_0)$ の加算をし、4ビットの数 $S=(S_3, S_2, S_1, S_0)$ を出力する回路である。この組み合わせ回路をDフリップフロップを用いて、3段のパイプライン動作するように回路変更せよ。部分点も加算るので、白紙ではなく回路を書くこと!(24点)