## 繰り返し処理とパイプライン処理

---

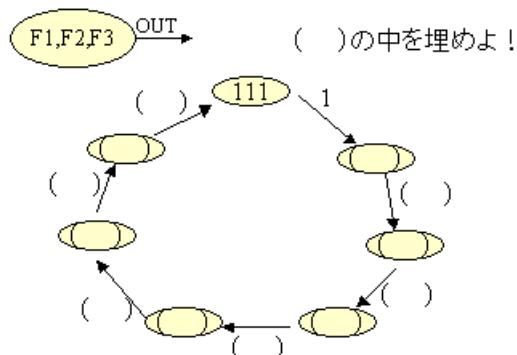

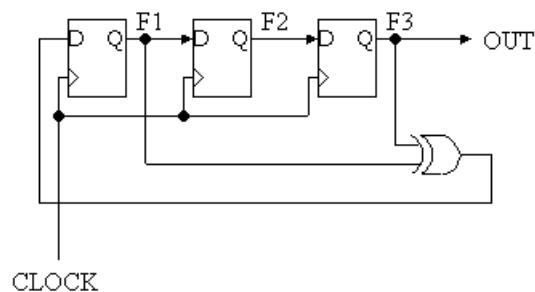

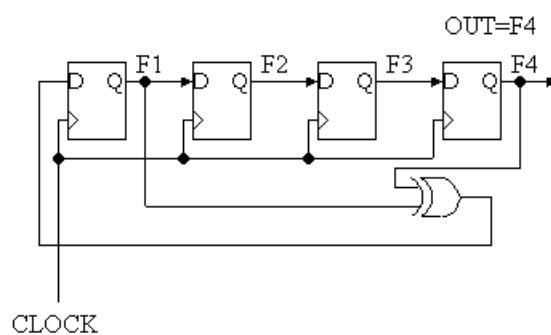

### ある状態遷移マシン(リニア・フィードバック・シフトレジスタ)

(例題)以下の回路の状態遷移図を完成させよ。但し、各D-FFの初期値はすべて1とする。

- この回路は実は、CDMA携帯電話での各ユーザを区別するための番号を生成する回路を小規模にしたものである。

-

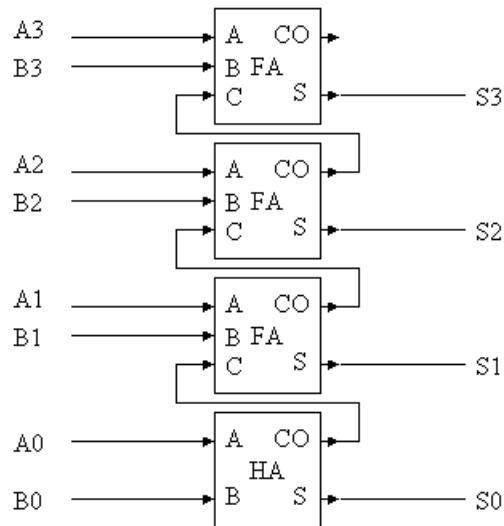

### 4ビット加算器の復習

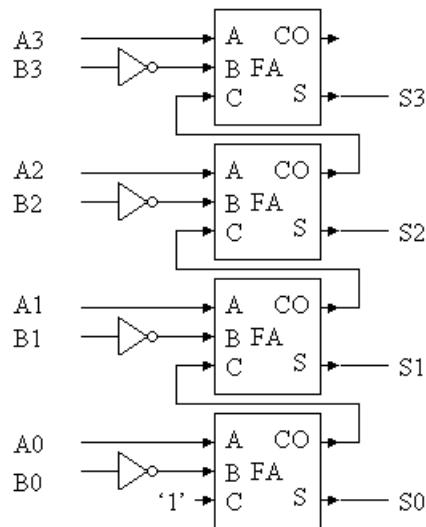

- 以下が、4ビットの数  $A = (A_3, A_2, A_1, A_0)$  と  $B = (B_3, B_2, B_1, B_0)$  を加算する回路であった。

- 和は  $S = (S_3, S_2, S_1, S_0)$  になる。

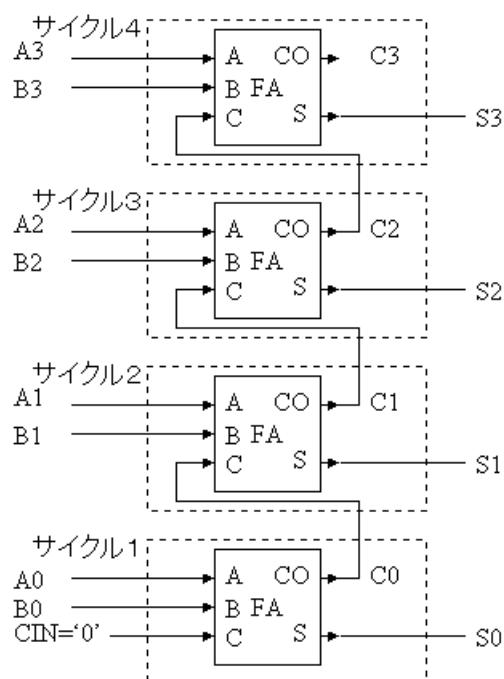

- 次にこれを以下のように、すべてフルアダーモード構成する。

- そうすると、各桁すべて同じ回路が使われていることになる。したがって、この4つのフルアダーモードを1つにし、1サイクル目でS0, COを計算し、次サイクルでS1, C1を計算し、3サイクル目でS2, C2を計算し、4サイクル目でS3, C3を計算することが可能である。

- ここで、1サイクル目の出力COを2サイクル目の入力にする必要があります。ここで、D-FにCOを記憶させる必要があります。

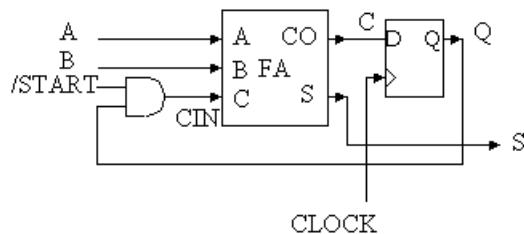

### 繰り返し型の4ビット加算器

- ということで、以下のようにすると、4サイクルで4ビットの加算が可能である。

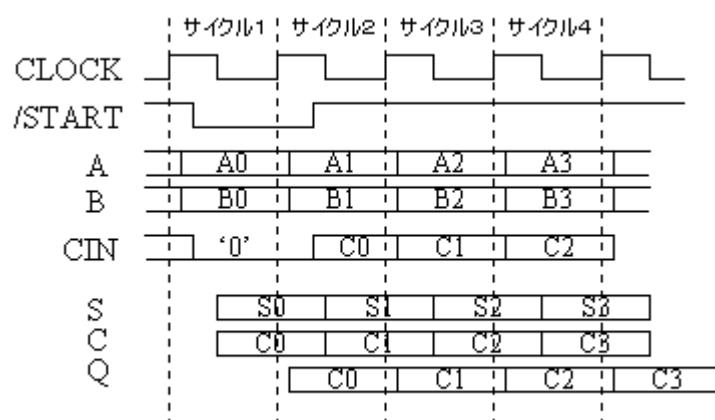

- 以下の図が動作波形図である。

|       |                                                        |

|-------|--------------------------------------------------------|

| サイクル1 | /START=0 であるので、CIN=0 となり、A0, B0, CIN入力より、S0, COが計算される。 |

| サイクル2 | /START=1 であるので、CIN=CO となり、A1, B1, CO入力より、S1, C1が計算される。 |

| サイクル3 | サイクル2と同様に、A2, B2, C1入力より、S2, C2が計算される。                 |

| サイクル4 | サイクル2と同様に、A3, B3, C2入力より、S3, C3が計算される。                 |

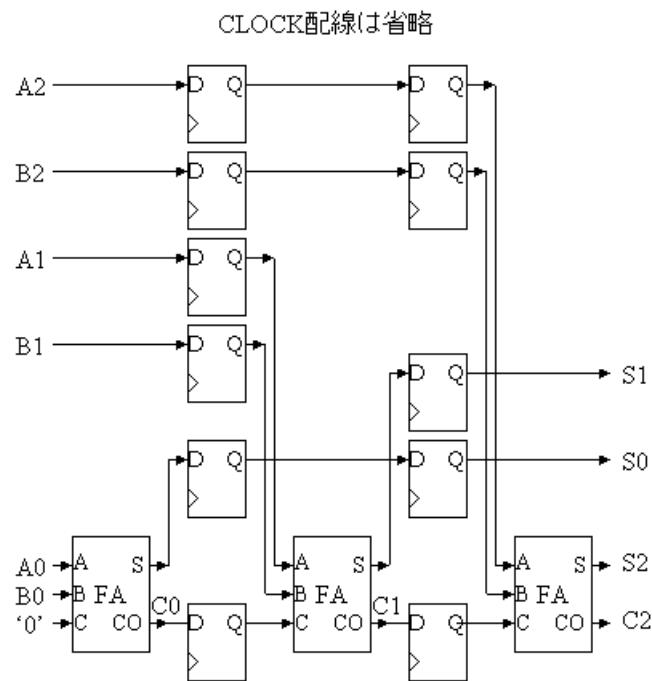

### パイプライン型3ビット加算器

- ちょっと複雑であるが、以下のようなことも可能です。

- これは3ビットの加算器で、A=(A2, A1, A0)、B=(B2, B1, B0)の2入力を入れた後、

- 2サイクル後に結果 $S=(S_2, S_1, S_0)$ と $C_2$ が output されます。

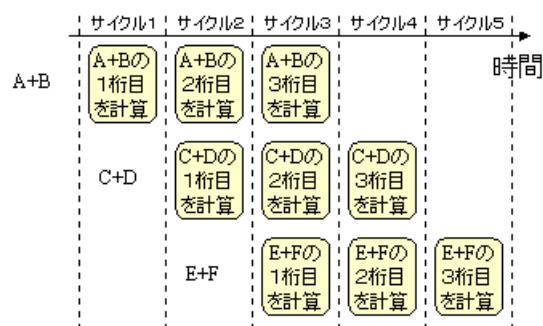

- 入力は実は毎サイクル入れてもOKです。以下に動作概念図を示します。

**宿題9 学籍番号 名前 日付 を書いて 提出すること。**

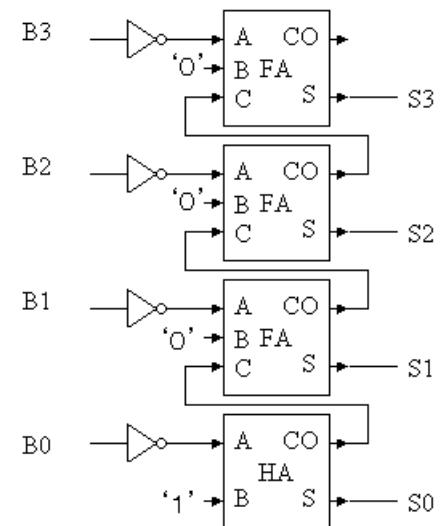

1)右下の図は、4ビットの数 $A = (A_3, A_2, A_1, A_0)$ と $B = (B_3, B_2, B_1, B_0)$ から $A - B$ を計算する減算器である。これを4サイクルで動作する繰り返し型の4ビット減算器に設計変更せよ。

2)上記設計変更した回路の動作波形を示せ。

3)下記のリニア・フィードバック・シフト・レジスタの状態遷移図を示せ。全部で何種類の状態が存在するか？

但し、各D-FFの初期値はすべて1とする。

4)フルアダーモしくはハーフアダーモ1つと少しの基本ゲートを用いて、4サイクルで動作する繰り返し型の4ビットの2の補数発生器を設計せよ。(ヒント：2の補数器は以下のようになる。)

以上