## 第9章 メモリとプログラマブルデバイス

### 1. RAM (Random Access Memory)

○ 2次元アレイ状に並んだ、1ビット記憶のひとつを、アドレス信号により指定して、記憶データを読み出すか、もしくは外部からデータを書き込むことができる。このような高速な読み出し、書き込みを“ランダムアクセス”と呼ぶ。

○ 電源を切ると、一般にはデータが消滅する(揮発性)である。

(a) SRAM 図9・1

1ビットのメモリは NOT ゲート 2 個と NMOS 2 個が一般的

D-FF を 2 次元的に配置しても実現できる。

特徴: DRAM に比べて、1ビットメモリの回路規模が大きく、高コストであるが高速性があるので、コンピュータキッシュメモリや、小規模高速メモリ用途に使用される。

(b) DRAM 図9. 3

1ビットのメモリはコンデンサ 1 個と NMOS1 個が一般的

○コンデンサにより微小な電荷を蓄積することで、'1' か '0' の情報を記憶する。

○上記微小電荷は漏れ電流により時間とともに減少するので、“リフレッシュ”と呼ばれる動作「データを読み出して、再度書き込みをする」を行っている。

問1. D-FF を用いて、16ビットの SRAM メモリを設計せよ。

クロック信号を CLK

アドレス信号を A0, A1, A2, A3

書き込み・読み出し制御信号を  $\overline{WE}$

データ入力を DIN

データ出力を DOUT

とする。

## 2. ROM (Read Only Memory)

RAM と同様にランダムアクセス可能であるが、書き込みが低速等など制限がある。

ROM は電源を切ってもデータが消失しない。(不揮発性という)

### (a) マスク ROM

工場出荷時に、記憶データを決める配線構造等が決められたもの。ユーザは記憶データの変更ができない。(昔のゲームカセット)

### (b) フラッシュメモリ

データ消去をブロック単位で行い、データの書き込みは RAM に比べては遅いが、ある程度高速なメモリ。不揮発性。(USB メモリ、デジカメの記憶媒体)

問2. フラッシュメモリのメモリセル(1 ビットを記憶する部分)の構造はどのようなものか？

## 3. プログラマブルデバイス

論理回路の機能をデータを設定することで、プログラマブルに実現できるデバイス。

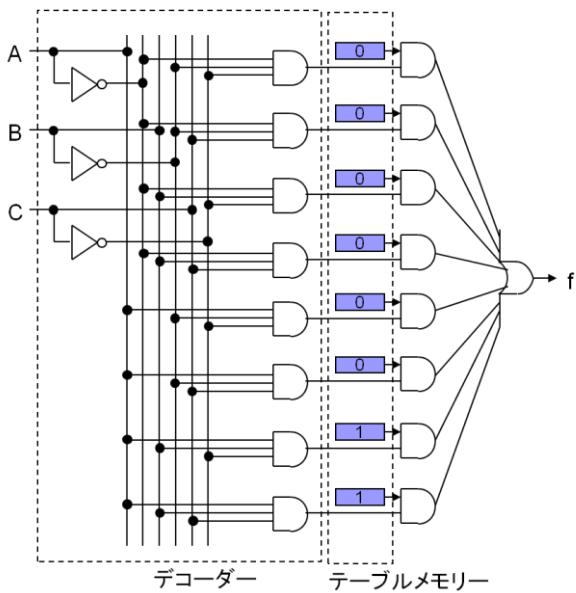

### (a) LUT による組み合わせ回路の実現

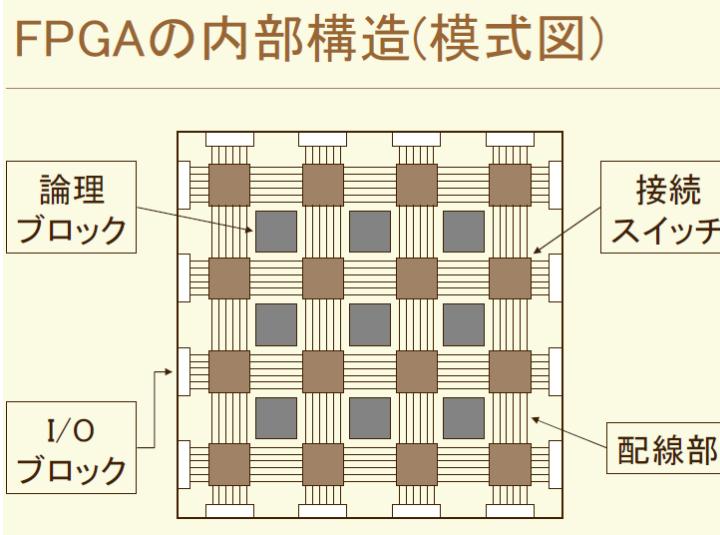

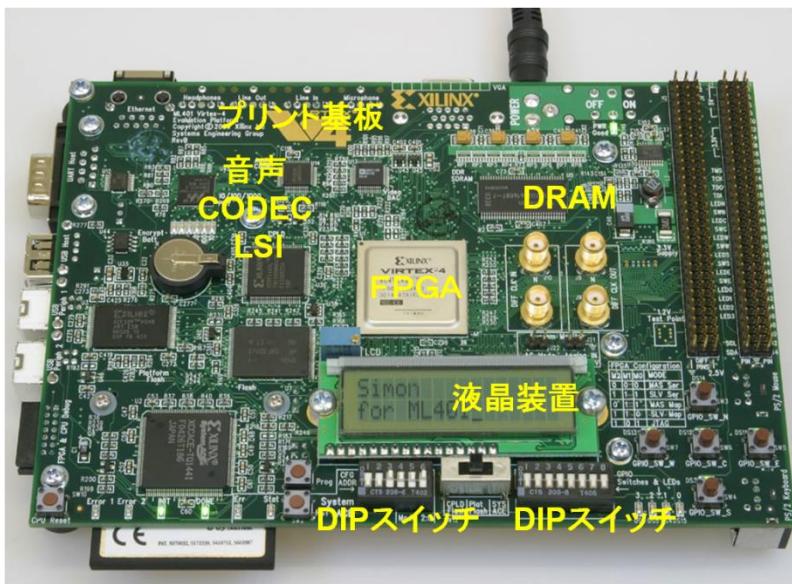

(b) FPGA の構造

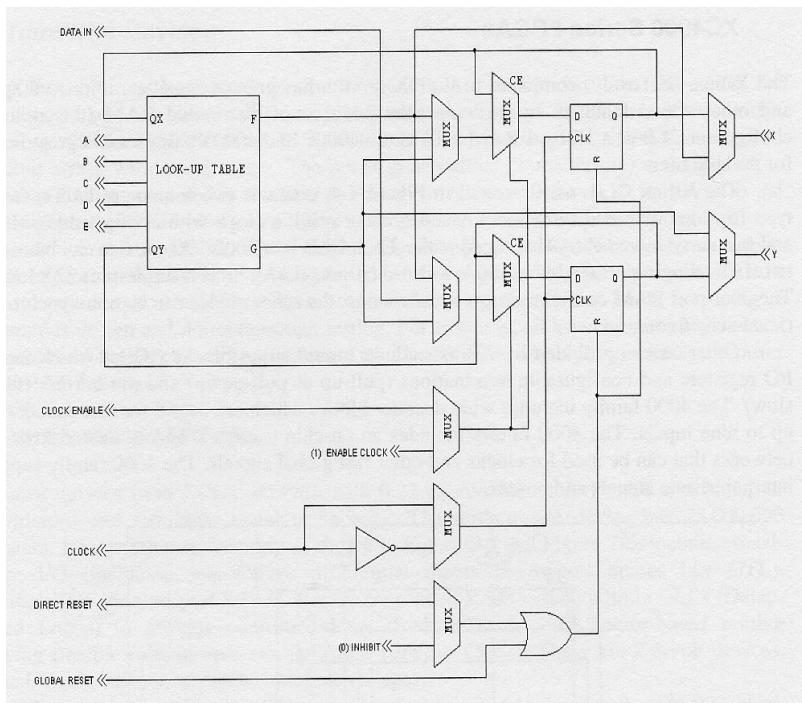

論理ブロックの例

CLB: Configurable Logic Block

Look-up table for combinational logic

D-Flip-Flops

Look-up Table

---

### 宿題10 学籍番号 名前 日付 を書いて 提出すること。

1) D-FF を用いて、16 ビットの SRAM メモリを設計せよ。

クロック信号を CLK

アドレス信号を A0, A1, A2, A3

書き込み・読み出し制御信号を

データ入力を DIN

データ出力を DOUT とする。

2) フラッシュメモリのメモリセル(1 ビットを記憶する部分)の構造はどのようなものか？

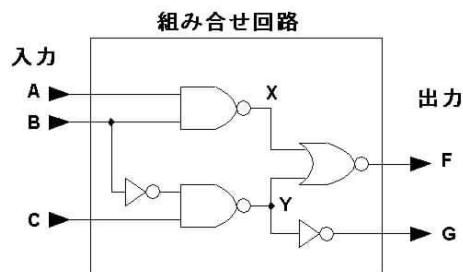

3) 以下の組み合わせ回路を LUT 方式の組み合わせ回路で実現せよ。

以上