### 本講座の内容

- ① FPGAの概要

- 2 LM4550 Audio Codec の概要

- ③ LM4550ドライバの概要

#### **FPGA**

- ✓ FPGA (field programmable gate array)

- ◆ 汎用LSIとASICの中間に位置するIC

- ◆ ユーザが所望する機能を自分で自由にプログラムできるIC

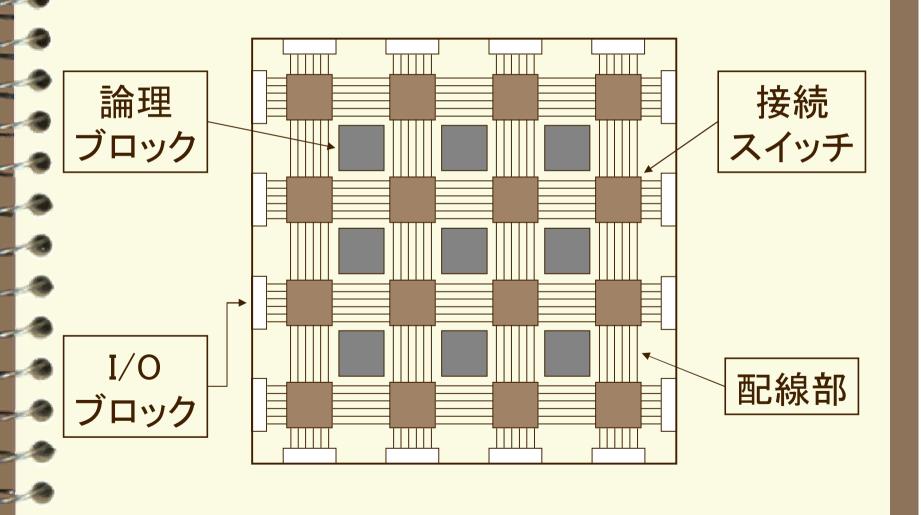

# FPGAの内部構造(模式図)

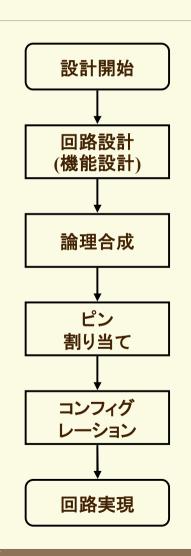

### FPGAへの回路実装手順

- 1. 回路設計: FPGAに実装する回路 を設計する

- 2. 論理合成:設計した回路をFPGA 用の設計ツールを用いて論理合 成する

- 3. ピン割り当て: 設計した回路の入 出力ポートとFPGAの端子(ピン)の 対応を付ける

- 4. コンフィグレーション: コンフィグレーションデータを生成し、FPGAに書き込む

#### 回路設計

- ✓ 回路設計は、以下のいずれかの方法に よって行う(ツールにより異なる)

- ▶ 回路図を描画する

- ➤ VHDLで記述する

- ➤ Verilog HDLで記述する

### 論理合成

- ✓ FPGA向けの論理合成をする場合、専用の設計ツールを用いる(無償ツール)

- ➤ XILINX社のFPGAの場合

ISE WebPACK

ALTERA社のFPGAの場合Quartus II Web Edition

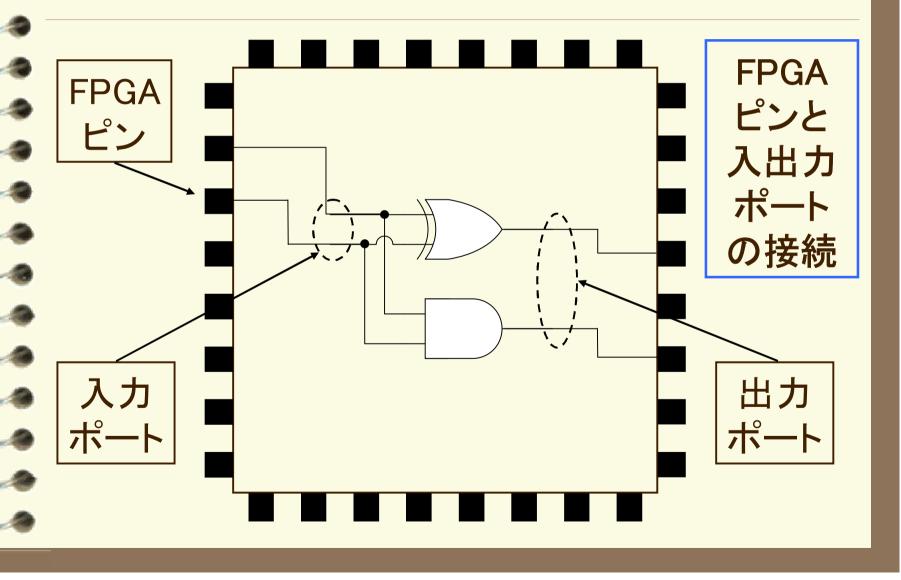

# ピン割り当て

### コンフィグレーション

PC

FPGAボード

パラレル ケーブル

コンフィグレーションデータ をFPGAに転送する

合成結果とピン割り当ての情報

### 本講座の内容

- ① FPGAの概要

- ② LM4550 Audio Codec の概要

- ③ LM4550ドライバの概要

### FPGAボードの概要

✓ Xilinx, Inc. 製

#### ML403 Evaluation Platform

- > FPGA: Xilinx Virtex-4

- ➤ クロック: 100 [MHz] オシレータ

- > メモリ: 64MB DDR SDRAM 他

- ▶ コネクタ: PS/2, USB, オーディオ 他

- ➤ ディスプレイ: 16×2 キャラクタLCD

- ➤ コンフィグレーション:パラレル(JTAG)

## FPGAボードの概観

仕様書 P. 2, 7 ~ 9, 12, 13 および接続図 参照

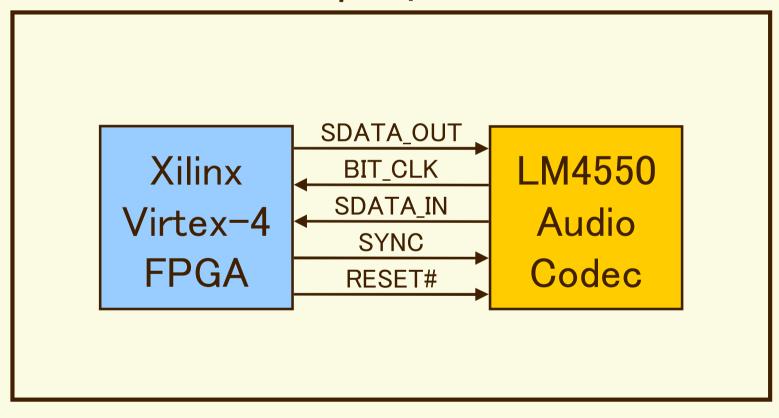

### FPGAとCodecの接続

#### FPGAボード ML403

# LM4550のデータ転送プロトコル

- ✓ LM4550のデータ転送は、フレームと呼ばれる単位で行われる

- ▶ 各フレームは、256clkの長さを持ち、さらに、 13個のスロットに分割される

- Slot0: Tag フェーズ、16clk

- Slot1~Slot12: Data フェーズ、各20clk

- ➤ ドライバ(FPGA) → LM4550 : SDATA\_OUT

- ► LM4550 → ドライバ(FPGA): SDATA\_IN

### 演習で使用するスロット

- ✓ SDATA\_OUT

- ➤ Slot0 ~ Slot4 を使用する

- ・ドライバは、これらのスロットの情報を、送信フレームに設定してから出力する必要がある

- ✓ SDATA\_IN

- > Slot3, Slot4 を使用する

- ・ドライバは、これらのスロットの情報を、受信フレームから取り出す必要がある

### SDATA\_OUT O Slot0

- ✓ フレーム全体の情報を示すタグ

- ▶ 本演習では、常に

"1111\_1000\_0000\_0000"(2進数)

を設定する

#### SDATA\_OUT O Slot1, 2

- ✓ LM4550に対する命令を保持するスロット

- ➤ Slot1: LM4550の内部レジスタのアドレス

- ➤ Slot2: そのレジスタに格納するデータ

- ▶ 本演習では、以下のレジスタのみ用いる

- Master Volume (アドレス: 02h)

- PCM Out Volume (アドレス: 18h)

- Record Select (アドレス: 1Ah)

- Record Gain (アドレス: 1Ch)

#### SDATA\_OUT O Slot3, 4

- ✓ PCMデータを保持するスロット

- ➤ Slot3: 左チャネルのPCMデータ

- ➤ Slot4:右チャネルのPCMデータ

- ➤ LM4550の D/A コンバータの精度は 18 ビットなので、各スロットの上位 18 ビットにPCM データを保持し、下位 2 ビットは 0 とする

### SDATA\_IN O Slot3, 4

- ✓ PCMデータを保持するスロット

- ➤ Slot3: 左チャネルのPCMデータ

- ➤ Slot4:右チャネルのPCMデータ

- ➤ LM4550の A/D コンバータの精度は 18 ビットなので、各スロットの上位 18 ビットにPCM データが格納され、下位 2 ビットは 0 となっている

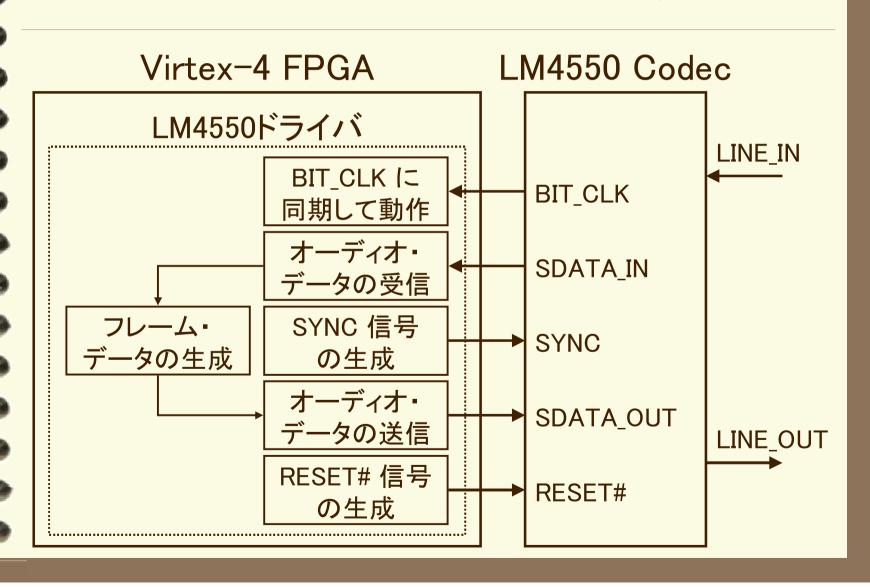

### BIT\_CLK 信号

- ✓ LM4550が生成する 12.288 [MHz] クロック

- ➤ LM4550には、24.576 [MHz] の水晶発振子が接続されており、これを分周して出力している

- ▶ ドライバは、この BIT\_CLK を使用して、同期 式回路として設計されている

### SYNC 信号

- ✓ ドライバが生成するフレーム同期信号

- ➤ SDATA\_OUT の Slot0 の期間中 SYNC = 1 と する必要がある

- ➤ LM4550は、この SYNC 信号に同期させて、 SDATA\_IN を出力する

#### RESET# 信号

- ✓ ドライバが生成するLM4550の初期化信号

- ➤ RESET# = 0 で、LM4550が初期化される

- ▶ 本演習では、常に

RESET# = 1

とする

### 本講座の内容

- ① FPGAの概要

- 2 LM4550 Audio Codec の概要

- ③ LM4550ドライバの概要

# LM4550ドライバの動作概要

# 設計済みドライバの構成

#### ✓ 階層構造とファイル名

|                                 | 第一階層                                       | 第二階層                               | 第三階層                                                     |

|---------------------------------|--------------------------------------------|------------------------------------|----------------------------------------------------------|

|                                 |                                            |                                    | frame_counter.vhd<br>(frame_counter)<br>有り               |

| ファイル名<br>(エンティティ名)<br>テストベンチの有無 |                                            |                                    | frame_out_ctrl.vhd<br>(frame_out_ctrl)<br>無し             |

|                                 | codec_drv_top.vhd<br>(codec_drv_top)<br>無し | codec_drv.vhd<br>(codec_drv)<br>有り | serial_parallel_conv.vhd<br>(serial_parallel_conv)<br>有り |

|                                 |                                            |                                    | slot_in_ctrl.vhd<br>(slot_in_ctrl)<br>無し                 |

|                                 |                                            |                                    | slot_out_ctrl.vhd<br>(slot_out_ctrl)<br>無し               |

|                                 |                                            |                                    | parallel_serial_conv.vhd<br>(parallel_serial_conv)<br>有り |

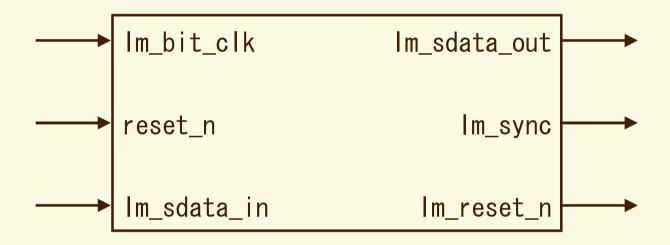

## codec\_drv\_top の概要(1)

✓ インターフェース

✓ 機能概要

ドライバ本体である codec\_drv コンポーネントに、 音量データ(m\_volume)を渡す回路

# codec\_drv\_topの概要(2)

| NAME         | 1/0 | WIDTH | DESCRIPTION                                |

|--------------|-----|-------|--------------------------------------------|

| lm_bit_clk   | IN  | 1     | LM4550が生成する 12.288 [MHz] クロック (ポジティブエッジ動作) |

| reset_n      | IN  | 1     | FPGAボード上のCPUリセットボタン(押すとリセット)               |

| lm_sdata_in  | IN  | 1     | LM4550から出力されるフレームのシリアル・データ                 |

| lm_sdata_out | OUT | 1     | LM4550に出力するフレームのシリアル・データ                   |

| lm_sync      | OUT | 1     | LM4550に出力する SYNC 信号 (SlotO の期間中 1 となる信号)   |

| lm_reset_n   | OUT | 1     | LM4550の初期化信号(常に 1 を出力)                     |

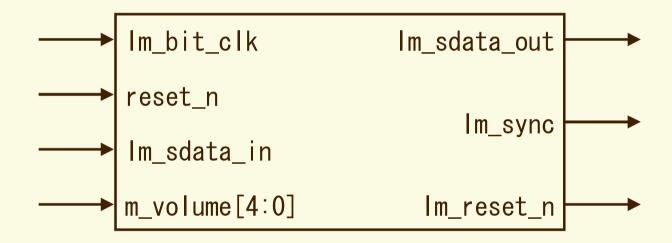

### codec\_drv の概要(1)

#### ✓ インターフェース

#### ✓ 機能概要

LM4550へSYNC信号(Im\_sync)を送信し、フレームデータを送受信する回路(ドライバ本体)

# codec\_drv の概要(2)

| NAME         | 1/0 | WIDTH | DESCRIPTION                                |

|--------------|-----|-------|--------------------------------------------|

| lm_bit_clk   | IN  | 1     | LM4550が生成する 12.288 [MHz] クロック (ポジティブエッジ動作) |

| reset_n      | IN  | 1     | FPGAボード上のCPUリセットボタン(押すとリセット)               |

| lm_sdata_in  | IN  | 1     | LM4550から出力されるフレームのシリアル・データ                 |

| m_volume     | IN  | 5     | 音量データ(減衰量を指定)                              |

| lm_sdata_out | OUT | 1     | LM4550に出力するフレームのシリアル・データ                   |

| lm_sync      | OUT | 1     | LM4550に出力する SYNC 信号 (Slot0 の期間中 1 となる信号)   |

| lm_reset_n   | OUT | 1     | LM4550の初期化信号(常に 1 を出力)                     |

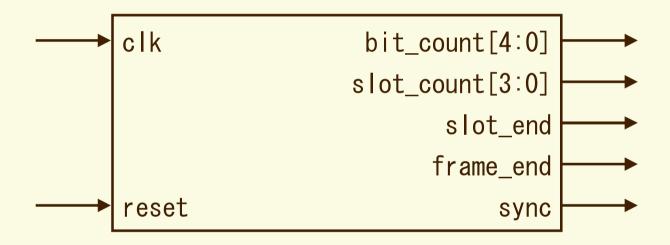

### frame\_counter の概要(1)

✓ インターフェース

✓ 機能概要

スロット数およびスロット内のclk数をカウントする回路

# frame\_counter の概要 (2)

| NAME       | 1/0 | WIDTH | DESCRIPTION                                                                     |

|------------|-----|-------|---------------------------------------------------------------------------------|

| clk        | IN  | 1     | LM4550が生成する 12.288 [MHz] クロック (ポジティブエッジ動作)                                      |

| reset      | IN  | 1     | FPGAボード上のCPUリセットボタン(押すとリセット)                                                    |

| bit_count  | OUT | 5     | スロット内の現在のビット位置を表す信号(0 = "00000" から 19 = "10011" までの値をとる信号)                      |

| slot_count | OUT | 4     | フレーム内の現在のスロット番号を表す信号(Slot0 から Slot12 に対応する 0 = "0000" から 12 = "1100" までの値をとる信号) |

| slot_end   | OUT | 1     | LM4550に出力するフレーム内の各スロットの終了位置を表す信号(各スロットの最終ビットで 1 となる信号)                          |

| frame_end  | OUT | 1     | LM4550に出力するフレームの終了位置を表す信号 (フレームの最終ビットで 1 となる信号)                                 |

| sync       | OUT | 1     | LM4550に出力する SYNC 信号 (SlotO の期間中 1 となる信号)                                        |

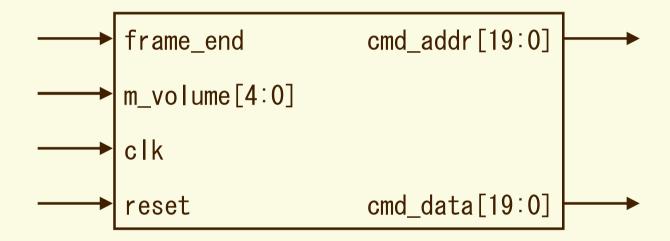

## frame\_out\_ctrl の概要(1)

#### ✓ インターフェース

#### ✓ 機能概要

Record Select, Record Gain, PCM Out Volume, Master Volume を順に設定する回路

# frame\_out\_ctrl の概要 (2)

| NAME      | 1/0 | WIDTH | DESCRIPTION                                     |

|-----------|-----|-------|-------------------------------------------------|

| frame_end | IN  | 1     | LM4550に出力するフレームの終了位置を表す信号 (フレームの最終ビットで 1 となる信号) |

| m_volume  | IN  | 5     | 音量データ(減衰量を指定)                                   |

| clk       | IN  | 1     | LM4550が生成する 12.288 [MHz] クロック (ポジティブエッジ動作)      |

| reset     | IN  | 1     | FPGAボード上のCPUリセットボタン(押すとリセット)                    |

| cmd_addr  | OUT | 20    | LM4550の内部レジスタのアドレス                              |

| cmd_data  | OUT | 20    | LM4550の内部レジスタに格納するデータ                           |

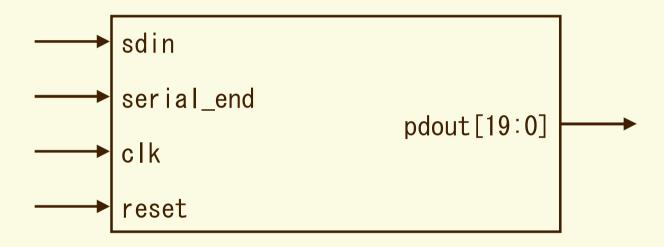

### serial\_parallel\_conv の概要(1)

✓ インターフェース

✓ 機能概要

シリアル・データをパラレル・データに変換する 回路

## serial\_parallel\_conv の概要 (2)

| NAME       | 1/0 | WIDTH | DESCRIPTION                                  |

|------------|-----|-------|----------------------------------------------|

| sdin       | IN  | 1     | LM4550から受信したシリアル・データ                         |

| serial_end | IN  | 1     | シリアルーパラレル変換の区切りを表す信号(slot_end 信号を遅延させた信号)    |

| clk        | IN  | 1     | LM4550が生成する 12.288 [MHz] クロック (ポジティブエッジ動作)   |

| reset      | IN  | 1     | FPGAボード上のCPUリセットボタン(押すとリセット)                 |

| pdout      | OUT | 20    | LM4550から受信したシリアル・データを、スロット単位でパラレル・データに変換した信号 |

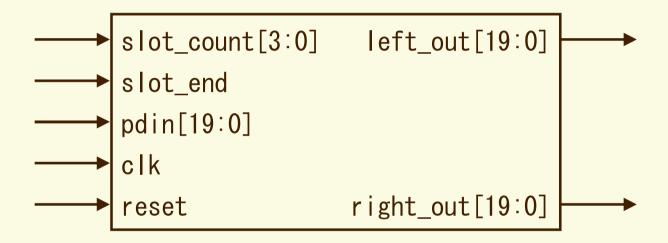

### slot\_in\_ctrl の概要(1)

✓ インターフェース

✓ 機能概要

受信フレームから、左右のチャネルのPCMデータを取り出す回路

# slot\_in\_ctrl の概要(2)

| NAME       | 1/0 | WIDTH | DESCRIPTION                                                                      |

|------------|-----|-------|----------------------------------------------------------------------------------|

| slot_count | IN  | 4     | フレーム内の現在のスロット番号を表す信号 (Slot0 から Slot12 に対応する 0 = "0000" から 12 = "1100" までの値をとる信号) |

| slot_end   | IN  | 1     | LM4550に出力するフレーム内の各スロットの終了位置を表す信号(各スロットの最終ビットで 1 となる信号)                           |

| pdin       | IN  | 20    | LM4550から受信したシリアル・データを、スロット単位でパラレル・データに変換した信号                                     |

| clk        | IN  | 1     | LM4550が生成する 12.288 [MHz] クロック (ポジティブエッジ動作)                                       |

| reset      | IN  | 1     | FPGAボード上のCPUリセットボタン(押すとリセット)                                                     |

| left_out   | OUT | 20    | LM4550から受信した左チャネルのPCMデータ                                                         |

| right_out  | OUT | 20    | LM4550から受信した右チャネルのPCMデータ                                                         |

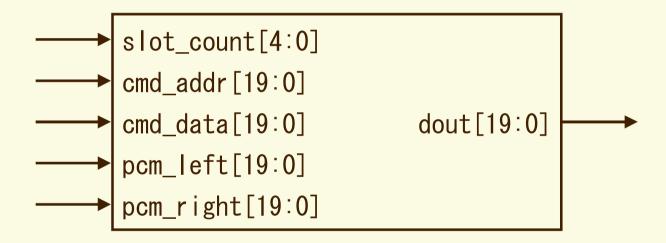

### slot\_out\_ctrl の概要(1)

✓ インターフェース

✓ 機能概要

スロット番号からスロット・データを生成する回路

# slot\_out\_ctrl の概要(2)

| NAME       | 1/0 | WIDTH | DESCRIPTION                                                                     |

|------------|-----|-------|---------------------------------------------------------------------------------|

| slot_count | IN  | 4     | フレーム内の現在のスロット番号を表す信号(Slot0 から Slot12 に対応する 0 = "0000" から 12 = "1100" までの値をとる信号) |

| cmd_addr   | IN  | 20    | LM4550の内部レジスタのアドレス                                                              |

| cmd_data   | IN  | 20    | LM4550の内部レジスタに格納するデータ                                                           |

| pcm_left   | IN  | 20    | LM4550に送信する左チャネルのPCMデータ                                                         |

| pcm_right  | IN  | 20    | LM4550に送信する右チャネルのPCMデータ                                                         |

| dout       | OUT | 20    | LM4550に送信するスロット・データ                                                             |

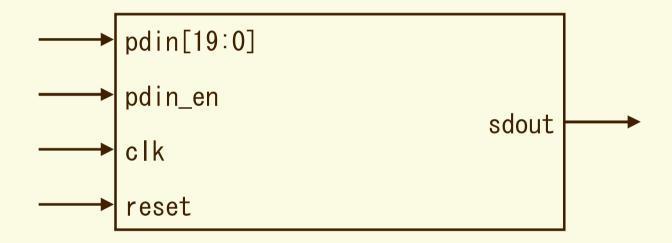

## parallel\_serial\_conv の概要(1)

✓ インターフェース

✓ 機能概要

パラレル・データをシリアル・データに変換する 回路

## parallel\_serial\_conv の概要 (2)

| NAME    | 1/0 | WIDTH | DESCRIPTION                                |

|---------|-----|-------|--------------------------------------------|

| pdin    | IN  | 20    | LM4550に送信するスロットのパラレル・データ                   |

| pdin_en | IN  | 1     | パラレルーシリアル変換の区切りを表す信号(slot_end 信号)          |

| clk     | IN  | 1     | LM4550が生成する 12.288 [MHz] クロック (ポジティブエッジ動作) |

| reset   | IN  | 1     | FPGAボード上のCPUリセットボタン(押すとリセット)               |

| sdout   | OUT | 1     | LM4550に送信するスロットのパラレル・データをシリアル・データに変換した信号   |