## ディジタルシステム設計 講義レジメ

## スタックに関する補足

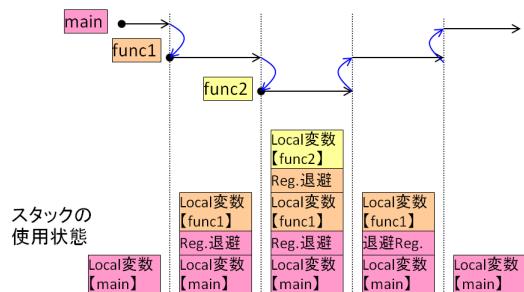

## ファンクション・コールとスタック (1/3)

- ・ファンクションから別ファンクションをコールするのは日常茶飯事

int func1(<arg>,<arg>){

//前処理

val = func2(<arg>,<arg>); //ファンクション・コール

//後処理

return (val)

}

- func1が「前処理」をした後、func1の実行を中断しfunc2が実行される。

- func2の実行が終わると、func1の「後処理」を再開する。

- ・中断したファンクションを、正しく再開するためには?

- 中途経過を安全な場所に保存しておく場所が必要。

- その保存場所が「スタック」と呼ばれるRAM上の領域。

- ・キーワード

- CPUのレジスタ(プログラムカウンタ、CPUステータス、汎用レジスタ、etc)

- 自動変数(ローカル変数)

## ファンクション・コールとスタック (2/3)

### ファンクション・コールとスタック (3/3)

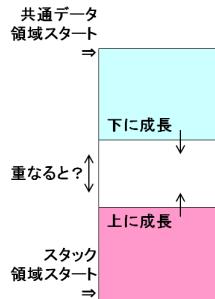

- ・ スタック破壊の可能性

- これが起きると暴走

- デバッグが難しい

- 避ける手段は？

- PCやLinuxの場合だと

- OSが領域をプロテクト

- Core Dumpして終了

### 1) システムデバッグ手法

図 7. 1

表 7. 1

## 2) シミュレータ

RTL

FPGA

3 ) JTAG ICE

### Column 7.A

4) FPGA とは プログラム（再構成）可能なデジタルシステムで、以下の部品を含む

①基本部品

組み合わせ回路

フリップ フロップ

プログラマブル配線

プログラマブル I/O 回路 (FPGA 外部との信号のやりとりをする)

プログラマブルクロック生成回路

②場合によって搭載される大規模部品

CPU

乗算器 (大規模な組み合わせ回路)

RAM ・ ROM

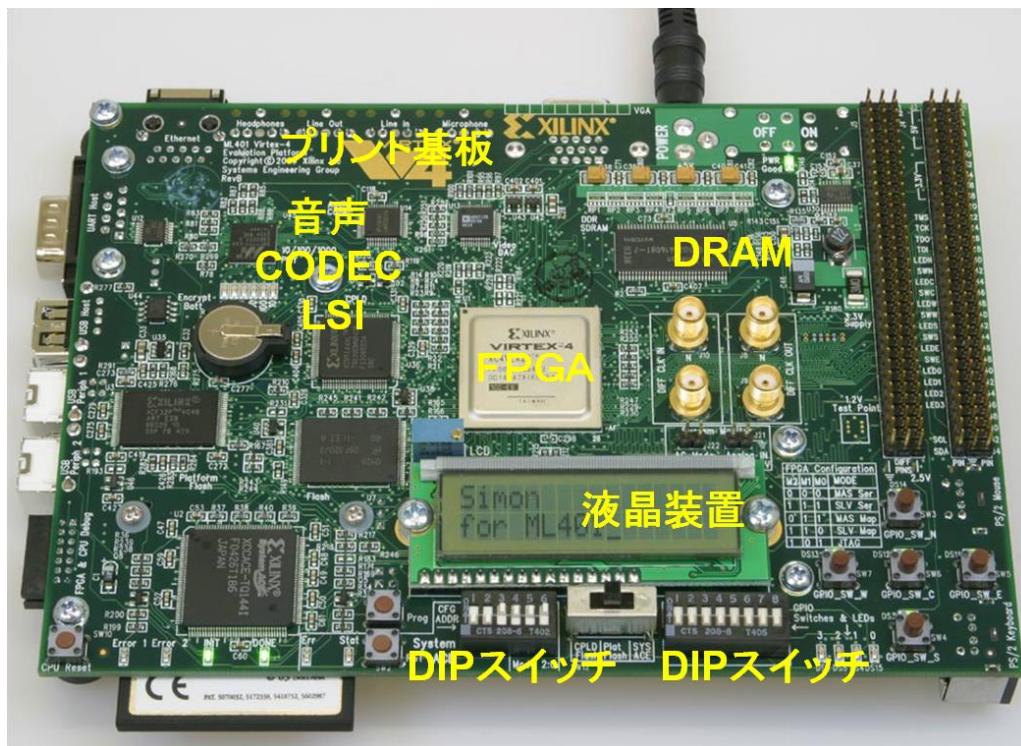

5) 後半の実習で使用するボード ML403 Evaluation Platform

①FPGA : フィールドプログラマブルゲートアレイ Xilinx Virtex-4

②音声 CODEC LM4550

③クロック: 100 [MHz] オシレータ

④メモリ: 64MB DDR SDRAM 他

⑤コネクタ: PS/2, USB, オーディオ他

⑥ディスプレイ: 16x2 キャラクタ LCD

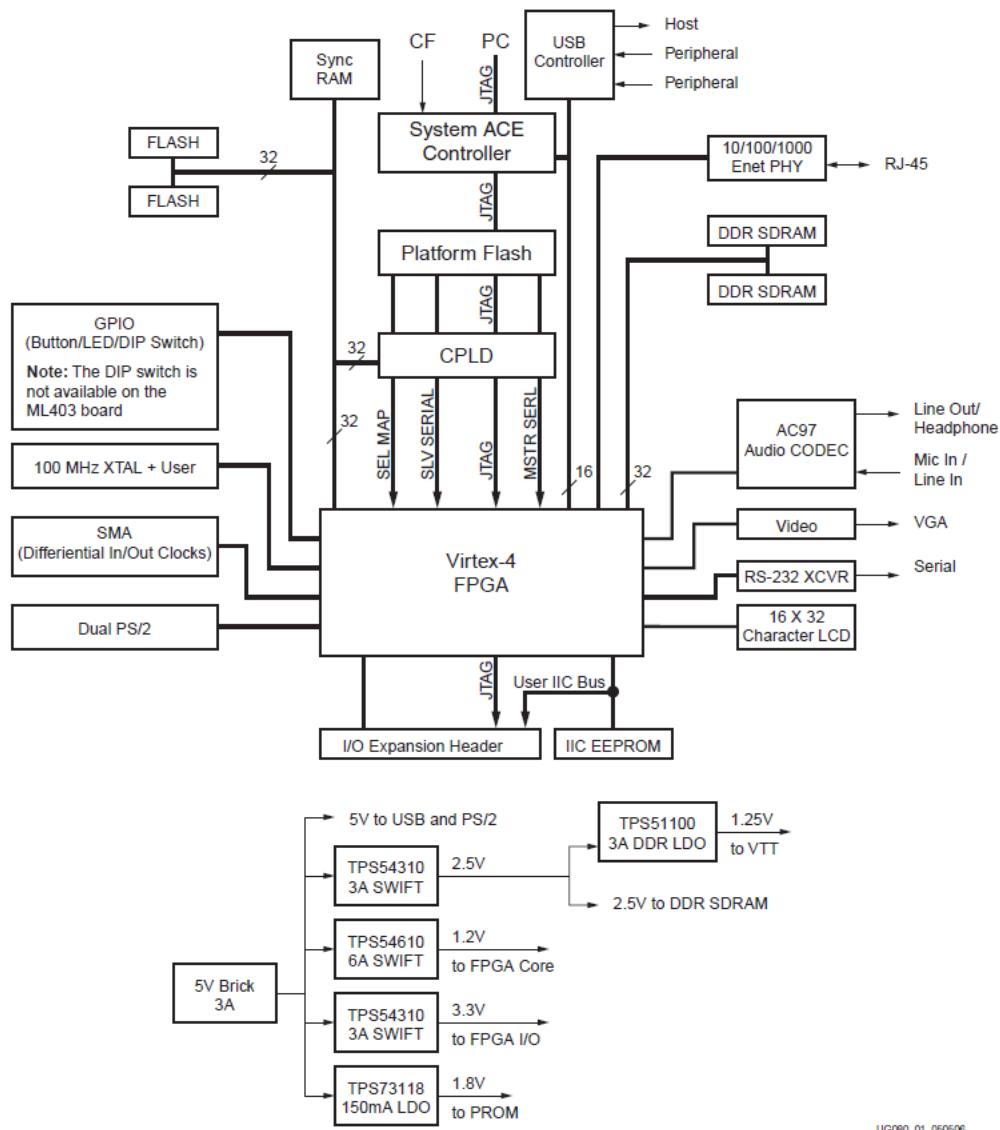

## Block Diagram

Figure 1 shows a block diagram of the ML40x evaluation platform (board).

Figure 1: Virtex-4 ML40x Evaluation Platform Block Diagram

音声 CODEC はどれか？

PC との接続ポートはどのようなものか？

GPIO とは何か？

FPGA のクロック入力は何 Hz か？

ボード内は何種類の電源電圧があるか？

外部ディスプレイを接続したければ、どこに接続すべきか？

FPGA 外部の大容量のメモリはどれか？

DMA コントローラはどこにあるのか？

PC の接続ポートは USB が主流であるが、どのようにこのボードの接続すべきか？

以上