EDITED BY FA-LONG LUO

# **Digital Front-End**

in Wireless Communications and Broadcasting

**Circuits and Signal Processing**

# 18 Diversity and error compensation in OFDM transceivers: principles and implementation

Tomohisa Wada

#### 18.1 Introduction

Digital modulation techniques can be largely divided into two categories. One is single-carrier modulation, which utilizes a single radio frequency (RF) to transmit data. The other is multi-carrier modulation, which utilizes simultaneously modulated multiple RF carriers in order to combat inter symbol interference (ISI) while increasing communication bandwidth. This chapter focuses on a particular type of multi-carrier modulation known as Orthogonal Frequency Division Multiplexing (OFDM). The idea of OFDM [1] was proposed in the 1960s followed a few years later by the Discrete Fourier Transform (DFT) based implementation algorithm [2]. Then, OFDM became practical and has been popular in a number of applications such as asymmetric digital subscriber line (ADSL), wireless local area network (WLAN), digital TV broadcasting (DTV). It also has become a strong candidate for 4th generation cellular land mobile radio system.

It is well known that OFDM modulation and demodulation can be implemented by IDFT and DFT. But in actual implementation, not only those DFTs but also several error compensation mechanisms are indispensable because orthogonality between parallel transmitted subcarrier signals are easily destroyed by synchronization errors such as RF error, clock sampling rate error, and FFT window position shift. When applying OFDM technology for mobile communication, Doppler induced RF errors easily distort a reception performance. Therefore the main contents of this chapter are two fundamental techniques to realize high-performance OFDM communication systems. These are Diversity technologies and Synchronization error Detection and Compensation methods. After this, real hardware implementation examples and their data are summarized.

The rest of this chapter is organized into five sections. Section 18.2 is devoted to presenting the principles and design of OFDM transceivers. Section 18.3 focuses on adaptive antenna array and several diversity techniques. In Section 18.4, we will deal with the detection and compensation of various error sources and practical factors. Section 18.5 presents the hardware implementation and related chip performance. In the final section, we will give a summary and there will be further discussion.

Digital Front-End in Wireless Communications and Broadcasting, ed. Fa-Long Luo. Published by Cambridge University Press. © Cambridge University Press 2011.

#### 18.2 OFDM transceivers: principles and design

#### 18.2.1 Single-carrier vs. multi-carrier modulation

In single-carrier modulation, data are sent in serial by modulating one single carrier frequency at a baud rate of R symbols per second. Then symbol length (1/R) has to be shortened in order to increase data transmission bandwidth as shown in Figure 18.1. However, wireless communication systems usually suffer from multipath fading. When the multipath delay time becomes significant compared with the symbol length, ISI happens and degrades wireless communication performance. Then it is not easy to increase the communication bandwidth by just reducing the symbol length.

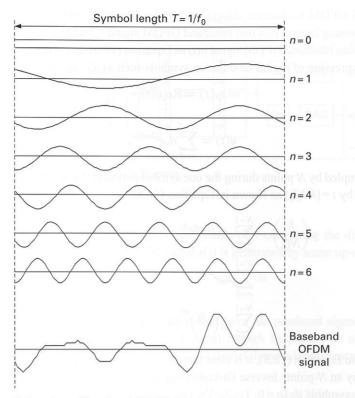

The idea of multi-carrier modulation is to use long symbol length against ISI but to use multiple carrier frequencies (called subcarriers) to increase the communication bandwidth. Figure 18.2 shows an example of a Baseband OFDM signal, which consists of n=0 to 6 seven sinusoids of frequency =  $n*f_0$  when symbol length  $T=1/f_0$ . By increasing the number of subcarriers, one symbol length can be kept long while achieving high bandwidth data transmission.

#### 18.2.2 OFDM signal generation

An OFDM signal consists of plural orthogonal carrier frequencies based on the following three orthogonal relations. In the equations, m and n are integers and  $T = 1/f_0$ .

Figure 18.1 Single-carrier modulation.

Figure 18.2 Subcarrier and baseband OFDM signal.

$$\int_0^T \cos(2\pi m f_0 t) \cdot \cos(2\pi n f_0 t) dt = \begin{cases} \frac{T}{2} & (m=n) \\ 0 & (m \neq n) \end{cases}$$

(18.1)

$$\int_{0}^{T} \sin(2\pi m f_{0}t) \cdot \sin(2\pi n f_{0}t) dt = \begin{cases} \frac{T}{2} & (m=n) \\ 0 & (m \neq n) \end{cases}$$

(18.2)

$$\int_{0}^{T} \cos(2\pi m f_{0}t) \cdot \sin(2\pi n f_{0}t) dt = 0.$$

(18.3)

One subcarrier signal, which is a basic component of the OFDM signal, in period [0, T] is expressed as Equation (18.4). In one symbol length T, precisely n cycles of sinusoid signal are included. By summing the N component signals, a baseband OFDM signal can be obtained as Equation (18.5). Here,  $f_0$  is neighboring subcarrier spacing:

$$a\cos(2\pi n f_0 t) - b\sin(2\pi n f_0 t)$$

(18.4)

$$s_B(t) = \sum_{n=0}^{N-1} \{ a_n \cos(2\pi n f_0 t) - b_n \sin(2\pi n f_0 t) \}.$$

(18.5)

In practical OFDM transceiver design, a complex baseband OFDM signal is used in signal processing instead of a real baseband OFDM signal  $s_B(t)$ , which can be shown by using complex baseband OFDM signal u(t) as Equation (18.6). In Equation (18.7),  $d_n$  is a complex expression of digital modulation symbols such as  $d_n = a_n + jb_n$ ,

$$s_B(t) = \text{Re}[u(t)] \tag{18.6}$$

$$u(t) = \sum_{n=0}^{N-1} d_n e^{j2\pi n f_0 t}.$$

(18.7)

If u(t) is sampled by N points during the one symbol period  $(1/f_0)$ , the time index t can be substituted by  $t = (k/Nf_0)$  as shown in Equation (18.8):

$$u\left(\frac{k}{Nf_0}\right) = \sum_{n=0}^{N-1} d_n e^{j2\pi n f_0 \frac{k}{Nf_0}}$$

$$= \sum_{n=0}^{N-1} d_n e^{j\frac{2\pi n k}{N}}$$

$$= \sum_{n=0}^{N-1} d_n \left(e^{j\frac{2\pi}{N}}\right)^{nk} (k = 0, 1, 2, \dots, N-1)$$

(18.8)

According to Equation (18.8), it is clear that the complex baseband OFDM signal can be generated by an N-points Inverse Discrete Fourier Transform (IDFT) of complex digital modulation symbols  $d_n$  (n = 0, 1, ..., N - 1).

The passband signal s(t) which is actually transmitted from an antenna is shown in Equation (18.9). Here,  $f_c$  is the minimum frequency of passband. Then, the passband signal consists of  $[f_c, f_c + 1f_0, f_c + 2f_0, \dots, f_c + (N-1)f_0]$  frequencies,

$$s(t) = \sum_{n=0}^{N-1} [a_n \cos\{2\pi (f_c + nf_0)t\} - b_n \sin\{2\pi (f_c + nf_0)t\}]$$

$$= \operatorname{Re} \left[ \sum_{n=0}^{N-1} d_n e^{j2\pi (f_c + nf_0)t} \right]$$

$$= \operatorname{Re} \left[ e^{j2\pi f_c t} \sum_{n=0}^{N-1} d_n e^{j2\pi nf_0 t} \right]$$

$$= \operatorname{Re} \left[ (\cos 2\pi f_c t + j \sin 2\pi f_c t) \sum_{n=0}^{N-1} d_n e^{j2\pi nf_0 t} \right]$$

$$= \cos 2\pi f_c t \cdot \operatorname{Re} \left[ \sum_{n=0}^{N-1} d_n e^{j2\pi nf_0 t} \right] + (-\sin 2\pi f_c t) \operatorname{Im} \left[ \sum_{n=0}^{N-1} d_n e^{j2\pi nf_0 t} \right]. \tag{18.9}$$

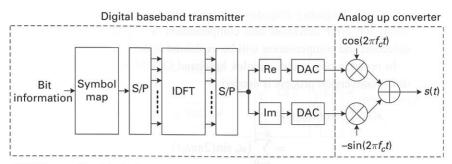

According to Equation (18.9), an OFDM transmitter block diagram is shown in Figure 18.3. First, bit information is mapped onto complex modulation symbols  $d_n$ . Then the serial-to-parallel converter makes an N-points symbol vector  $d_n$  (n=0, ..., N-1). By Inverse Discrete Fourier Transform, an OFDM complex baseband signal

Figure 18.3 OFDM transmitter block diagram.

$u(k/Nf_0)$  (k=0, ..., N-1) is generated. After converting the digital baseband signal to analog, a passband OFDM signal s(t) is generated by some up-converters.

#### 18.2.3 OFDM signal reception

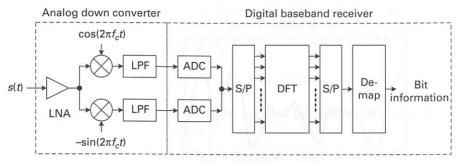

In this section, OFDM demodulation from the passband signal in Equation (18.10) is explained. Since the passband signal is high frequency, an analog down-conversion process is needed before the OFDM digital demodulation process

$$s(t) = \sum_{n=0}^{N-1} [a_n \cos\{2\pi (f_c + nf_0)t\} - b_n \sin\{2\pi (f_c + nf_0)t\}].$$

(18.10)

As shown in the following, a typical direct conversion performs the multiplication of  $f_c$  frequency sinusoids to passband signal and then passes a low-pass filtering.

$$s(t)2\cos(2\pi f_c t) = 2\sum_{n=0}^{N-1} [a_n \cos\{2\pi (f_c + nf_0)t\}\cos(2\pi f_c t) -b_n \sin\{2\pi (f_c + nf_0)t\}\cos(2\pi f_c t)]$$

$$= \sum_{n=0}^{N-1} \{a_n \cos(2\pi nf_0 t) - b_n \sin(2\pi nf_0 t)\}$$

$$+ \sum_{n=0}^{N-1} [a_n \cos\{2\pi (2f_c + nf_0)t\} - b_n \sin\{2\pi (2f_c + nf_0)t\}]$$

(18.11)

Then, by applying the low-pass filter to Equation (18.11), the  $2f_c$  component can be removed and the  $s_I(t)$  signal is obtained as Equation (18.12).

$$s_I(t) = \sum_{n=0}^{N-1} \{ a_n \cos(2\pi n f_0 t) - b_n \sin(2\pi n f_0 t) \}.$$

(18.12)

This signal is equivalent to the baseband OFDM signal in Equation (18.5). In this process, a precise  $f_c$  frequency sinusoid is used. In a general down-converter the local

oscillator's frequency includes frequency error or frequency drift on time. Then additional RF error detection and compensation is required. These topics on RF error detection and compensation will be explained in the following related sections.

In order to obtain the complex baseband OFDM signal as Equation (18.7), another down-conversion process is needed:

$$s(t)2\{-\sin(2\pi f_c t)\}$$

$$= \sum_{n=0}^{N-1} \{a_n \sin(2\pi n f_0 t) + b_n \cos(2\pi n f_0 t)\}$$

$$+ \sum_{n=0}^{N-1} [-a_n \sin\{2\pi (2f_c + n f_0)t\} - b_n \cos\{2\pi (2f_c + n f_0)t\}].$$

(18.13)

Again, by low-pass filtering,  $s_O(t)$  signals are obtained as Equation (18.14):

$$s_{Q}(t) = \sum_{n=0}^{N-1} \{a_n \sin(2\pi n f_0 t) + b_n \cos(2\pi n f_0 t)\}.$$

(18.14)

By combining  $s_l(t)$  and  $s_O(t)$ , a complex baseband signal u(t) can be obtained:

$$u(t) = s_I(t) + js_Q(t) = \sum_{n=0}^{N-1} (a_n + jb_n) \{\cos(2\pi n f_0 t) + j\sin(2\pi n f_0 t)\}$$

$$= \sum_{n=0}^{N-1} d_n e^{j2\pi n f_0 t}.$$

(18.15)

By a sampling process such as N-points during the one symbol period  $(1/f_0)$ , this equation can be converted as follows:

$$u\left(\frac{k}{Nf_0}\right) = \sum_{n=0}^{N-1} d_n \left(e^{j\frac{2\pi}{N}}\right)^{nk} \quad (k = 0, 1, 2, \dots, N-1)$$

(18.16)

As described in the previous section, this is an IDFT operation. Then the complex digital modulation symbol  $d_n$  (n = 0, 1, ..., N-1) can be calculated by Inverse IDFT operation, that is, Discrete Fourier Transform (DFT) as shown in Equation (18.17):

$$d_l = \frac{1}{N} \sum_{k=0}^{N-1} u \left( \frac{k}{Nf_0} \right) \left( e^{-\frac{j^2 \pi}{N}} \right)^{nk} \quad (l = 0, 1, 2, \dots, N-1)$$

(18.17)

In Figure 18.4, a simple OFDM receiver block diagram is shown. Here, it is assumed that the received OFDM signal is completely the same as the transmitted OFDM signal. However, in real wireless communication, the received signal is distorted. Then the OFDM receiver needs an additional signal processing block to remove the distortion such as an equalizer.

Figure 18.4 Simple OFDM receiver block diagram.

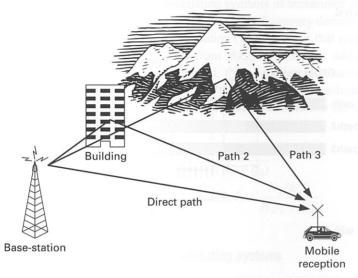

Figure 18.5 Multipath channel.

#### 18.2.4 Multipath channel

In the real wireless communication channel, the RF wave propagates in space where refraction and reflection exist. Multiple propagating paths (multipath) exist between transmitter antenna and receiver antenna as shown in Figure 18.5. Reflecting path2 and path3 are longer propagation paths compared with the direct path. Then at the receiver antenna, multiple delayed and phase-rotated signals are overlapped and cause ISI. Since OFDM is especially sensitive to ISI, a Guard Interval (GI) is usually inserted between OFDM symbols.

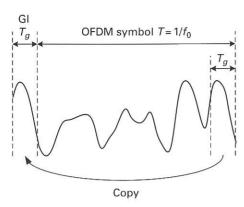

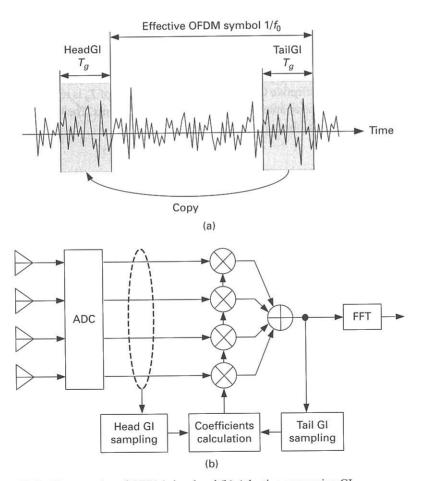

A typical guard interval between OFDM symbols is a copy of the tail part of the OFDM symbol as shown in Figure 18.6. Please note that the connection point between the GI and OFDM symbol is smoothly connected because all the components of the OFDM symbol have cycle times of  $1/(nf_0)$ . This type of guard interval is called cyclic prefix (CP). Since the insertion of the guard interval  $T_g$  reduces data rate, a shorter GI length is preferable. Typical GI length is 1/16 to 1/4 of OFDM symbol length  $T=1/f_0$ .

Figure 18.6 Guard interval.

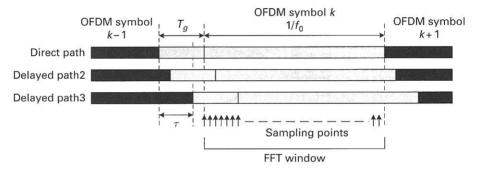

Figure 18.7 Multipath with GI

Figure 18.7 shows how the GI mitigates the ISI. An OFDM receiver performs FFT operation at the FFT window position. If a CP type GI is used and the maximum multipath delay path  $\tau$  is shorter than  $T_g$ , ISI can be removed perfectly and the orthogonality between subcarriers is maintained. Then the equalizer which removes the multipath distortion becomes very simple. However if zero signals (zero padding) are used in the GI period instead of CP, the orthogonality between subcarriers is destroyed and inter carrier interference (ICI) is generated. Then a complicated equalizer is required [3]. In this chapter, only CP type GI is assumed.

#### 18.2.5 Channel estimation and equalizer

Assuming that h(t) is the impulse response of a transmission channel for an OFDM signal, the reception signal  $s_R(t)$  can be expressed as follows using convolution:

$$s_R(t) = \int_{-\infty}^{\infty} h(u)s(t-u)du + n_c(t).$$

(18.18)

The first term is distortion caused by the multipath channel and the second term is noise addition in the OFDM communication frequency band. If the width of the channel impulse response h(t) is shorter than GI length  $T_g$ , the channel transfer function H(f) is given as:

$$H(f) = \int_{0}^{T_g} h(t)e^{-j2\pi ft}dt$$

(18.19)

Since a convolution operation can be replaced by multiplication after DFT, the following equation can be obtained:

$$x(k,l) = H(f_c + lf_0)d(k,l) + N_B(k,l),$$

(18.20)

where, k and l are symbol number and subcarrier number, respectively. The d(k,l) and x (k,l) are the complex digital modulation symbols of transmitter and receiver at symbol number k and subcarrier number l;  $N_B(k,l)$  is the frequency domain complex noise. Since  $H(f_c + lf_0)$  is a complex number, Equation (18.20) means that received symbol x(k,l) is distorted in amplitude and phase from d(k,l) and noise is added. Once the channel transfer function  $H(f_c + lf_0)$  is obtained, the original transmission symbol can be estimated by the following equation. This process is called equalization. Therefore, if the noise is enough small, the equalization process can recover the original symbol d(k,l) from the received symbol x(k,l):

$$\hat{d}(k,l) = \frac{x(k,l)}{H(f_c + lf_0)}$$

$$= d(k,l) + \frac{N_B(k,l)}{H(f_c + lf_0)}$$

(18.21)

#### 18.2.6 OFDM communication and broadcasting systems

Table 18.1 summarizes the state-of-the-art OFDM or OFDMA based communication and broadcasting systems. A wide variety of symbol lengths is used from 3.2  $\mu$ s to 1008  $\mu$ s for various applications. As explained in the previous section, GI length is related to the multipath delay profile. Then, the larger the service area becomes, the longer an OFDM

| Table 18.1 OF | DM applications | and effective | symbol | lenath. |

|---------------|-----------------|---------------|--------|---------|

|---------------|-----------------|---------------|--------|---------|

| Application of OFDM                   | Effective OFDM symbol length $1/f_0$ |  |

|---------------------------------------|--------------------------------------|--|

| WLAN (802.11 g/a/n)                   | 3.2 μs                               |  |

| XGP (eXtended Global Platform)        | 26.67 μs                             |  |

| 3.9G mobile phone LTE                 | 66.67 μs                             |  |

| WiMAX (802.16e)                       | 102.4 μs                             |  |

| 3.9G mobile phone LTE (Extended mode) | 133.33 μs                            |  |

| China Digital TV Broadcasting DTMB    | 500.0 μs                             |  |

| Europe Digital TV Broadcasting DVB-T  | 896 μs (8K mode)                     |  |

| Japan Digital TV Broadcasting ISDB-T  | 1008 μs (8K mode)                    |  |

symbol length is used. WLAN and three digital TV broadcasting systems are one-to-one data transfer at a time based on OFDM. XGP [4], LTE[5], and WiMAX [6] are one base-station to multiple user terminal communication based on Orthogonal Frequency Division Multiple Access (OFDMA).

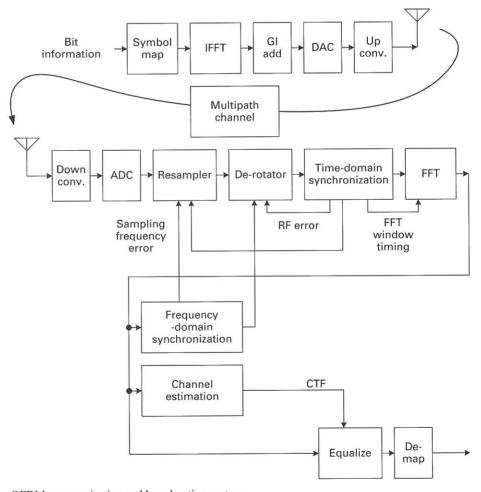

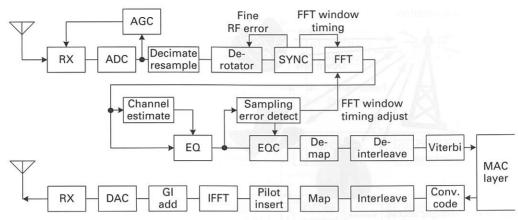

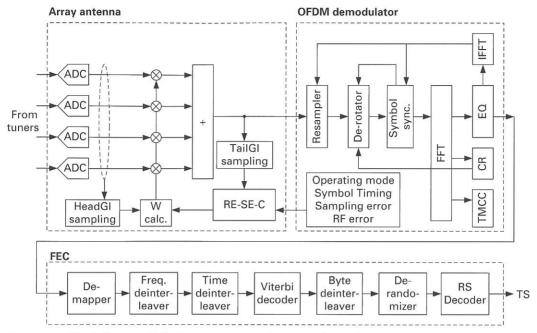

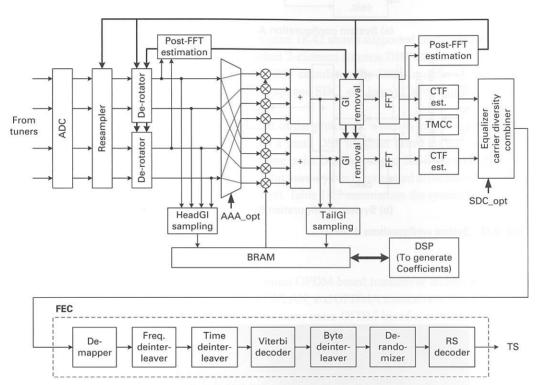

A more detailed OFDM communication and broadcasting system block diagram is shown in Figure 18.8. For the transmitter side, GI insertion is added to Figure 18.3. Since the receiver side needs synchronization to the transmitter, more blocks are added. The resampler represents the sampling frequency error compensation block. The de-rotator rotates the baseband OFDM signal to compensate for radio frequency error. The sampling frequency error is caused by system sampling clock accuracy. Then, in the case that enough high accuracy crystal oscillators are used in the system design, the resampler might not be needed. However, radio frequency error is caused by the frequency difference between up-conversion and down-conversion. Since the conversion frequency is as

Figure 18.8 OFDM communication and broadcasting system.

large as mega to giga Hz order, the frequency error usually exists and the de-rotator is always needed. Those synchronization error compensation issues will be covered in later sections. The FFT block needs to know the FFT window position as shown in Figure 18.7. Then the synchronization block also generates FFT window position timing:

- radio frequency (RF) synchronization

- · sampling rate synchronization

- symbol timing (FFT window position) synchronization.

These three synchronizations have to be considered to implement a real OFDM system. The channel transfer function (CTF) has to be estimated to remove the distortion by multipath channel. In Figure 18.8, the following synchronization functions are assumed as

- time domain RF and sampling rate error detection

- time domain symbol timing (FFT window position) detection

- frequency domain RF and sampling rate error detection

- frequency domain channel estimation.

In addition, time domain channel estimation and frequency domain symbol timing (FFT window position) detection are also possible. Suitable detection and estimation algorithms have to be applied depending on the applications.

#### 18.2.7 OFDM WLAN design

#### 18.2.7.1 WLAN system overview

The IEEE 802.11 standard WLAN is successfully utilized in the market. The first generation IEEE 802.11 standard was made at the end of 1996 to provide 1 or 2 Mbps in the 2.4 GHz Industry-Science-Medical (ISM) band. Later, in order to provide a higher data rate, the OFDM-based physical layer standard was established as IEEE 802.11a/g. Since 802.11a/g is based on distributed carrier sense multiple accesses with collision avoidance (CSMA/CA), in the wireless channel only one packet of OFDM signal is transmitted from one to another. Table 18.2 shows IEEE 802.11a/g OFDM based WLAN parameters. It supports from 6Mbps to 54Mbps data rates. The effective OFDM symbol

Table 18.2 OFDM WLAN parameters (802.11a/g).

| Data rate (Mbps)      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9    | 12   | 18   | 24    | 36    | 48    | 54    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------|-------|-------|

| Modulation            | BPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BPSK | QPSK | QPSK | 16QAM | 16QAM | 64QAM | 64QAM |

| Code rate             | 1/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3/4  | 1/2  | 3/4  | 1/2   | 3/4   | 2/3   | 3/4   |

| # of subcarriers      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      | 52    |       |       |       |

| # of pilots           | and a state of the second of t |      |      |      |       |       |       |       |

| OFDM symbol length    | 4 $\mu$ s (effective symbol = 3.2 $\mu$ s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |       |       |       |       |

| Guard Interval length | 0.8 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |      |      |       |       |       |       |

| Subcarrier spacing    | $312.5  \text{kHz} = 1/3.2  \mu \text{s}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |      |       |       |       |       |

| Sampling rate         | 20 MHz (50ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |      |       |       |       |       |

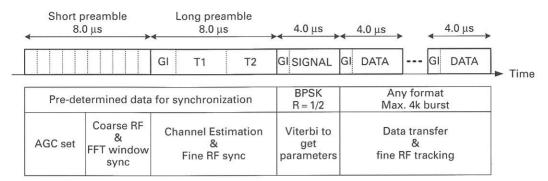

Figure 18.9 WLAN frame format and receiver tasks.

length is 3.2 µs. Since the sampling frequency is 20 MHz, 64 sampling points exist in one effective OFDM symbol. Then the demodulation process needs 64 point FFT.

#### 18.2.7.2 WLAN system architecture

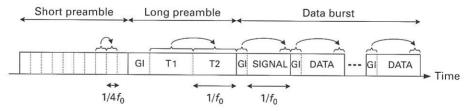

Figure 18.9 shows the frame format of a transmission packet. In addition, receiver tasks are indicated in the lower side of the figure. The first portion of the frame is a short preamble, which is composed of 0.8 µs pre-determined signals, repeated 10 times. During the former half periods of the short preamble, the auto gain control (AGC) value to the low-noise amplifier (LNA) in the analog front-end has to be determined. Since channel estimation is performed only once in the long preamble period in the WLAN system, the AGC control value has to be fixed in the short preamble period and has to be kept until the end of frame. Then during the latter half period of the short preamble, the RF error has to be measured and compensated by the de-rotator. Details of the RF error detection will be explained in Section 18.4. Then the end point of the short preamble has to be detected to get FFT window position for later OFDM symbols. In the long preamble, there are two identical 3.2 µs OFDM symbols T1, T2 and 1.6 µs GI. Using T1 to T2 rotation, a more precise RF error can be estimated (see Section 18.4.1). Since T1 and T2 are predetermined pilot OFDM symbols, CTF can be estimated from the FFT output of T2. This CTF value will be used in the following OFDM symbol equalization until the end of frame since WLAN assumes a NOT moving application such as fixed channel.

As for sampling frequency error, it is not easy to detect the error and compensate for it during the preambles since the preamble duration is limited. However, if less than  $100\,\mathrm{ppm}$  error crystal is used, a maximum  $64\times100\,\mathrm{ppm}=0.0064$  points sampling error is caused during one  $3.2\,\mu\mathrm{s}$  OFDM symbol. This 0.0064 points error in one OFDM symbol is sufficiently smaller than 1 percent error, then this sampling clock error does not cause an ICI problem. The 0.0064 points error will be accumulated in all successive OFDM data symbols with 4K being the maximum number of these symbols for accumulation. Then the accumulation of point shift

Figure 18.10 WLAN.

will be  $4K \times 0.0064 = 26$  points. Since the GI length is 16 points, this FFT window shift has to be taken care of. Therefore, the receiver needs to detect FFT window shift and compensate for it. Since the CTF value is estimated by T1, T2 at the long preamble and is used in the equalization process, the equalized output will be rotated by the FFT window position shift. Then, after a conventional equalizer (EQ), a FFT window shift detector and equalizer output compensator (EQC) is needed as shown in Figure 18.10. If high precision crystal is used, this special detector and compensator are not needed. However, analog down-conversion LO frequency might drift during the 4K OFDM symbols, and then the RF error tracking mechanism would be needed.

Figure 18.10 shows the block diagram of a WLAN transceiver. The RX is an analog front-end. By calculating the short preamble power, AGC feedback value to the LNA is determined. In the diagram, the decimate and resample block is assumed to be fixed rate. Since FFT size is as small as 64, the sampling clock frequency error does not have significant impact on ICI in one OFDM symbol. But an accumulated sampling error causes FFT window position shift, which causes equalizer output constellation rotation depending on the subcarrier number. Therefore in this design, the rotation compensation block EQC is included. The EQC process is further explained in Section 18.4.6. After the de-mapping process, forward error correction for convolutional code is performed using the famous Viterbi algorithm.

#### 18.2.8 OFDMA transceiver design

#### 18.2.8.1 OFDMA transceiver system overview

The abbreviation OFDMA represents Orthogonal Frequency Division Multiple Access. Then multiple users have to share OFDM subcarriers in a symbol. Figure 18.11 shows an example of wireless multiple access for mobile phones. First, Up-Link (UL) and Down-Link (DL) have to be separated. This separation is usually implemented by Frequency

Figure 18.11 Multiple access.

Figure 18.12 OFDMA power spectrums.

Division Duplex (FDD) or Time Division Duplex (TDD). The FDD needs two separate frequency bands although TDD has to share one frequency band by time slot. Secondly, multiple user communications have to be separated. This second separation can also be done by FDD or TDD method. However, this inter-user separation can be realized by OFDM technology, which is called OFDMA.

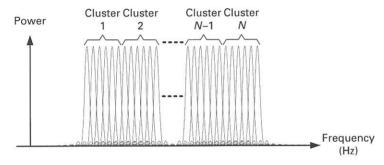

In an OFDMA communication system, many subcarriers are divided into plural clusters as shown in Figure 18.12. Those clusters are assigned to each user. During DL communication, all clusters are transmitted from base-station to users. Each user receives all clusters and demodulates assigned clusters. But in UL communication each user generates pre-assigned cluster subcarriers and the base station receives summed cluster subcarriers from all users.

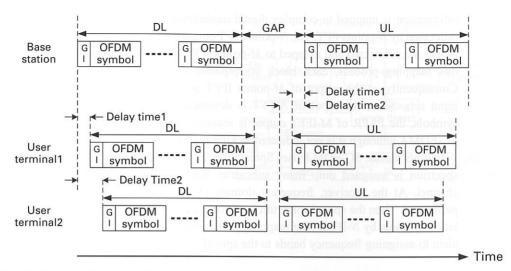

Figure 18.13 shows a TDD Frame structure for one base-station (BS) and two user terminals U1, U2. Delay time1 and 2 are wireless propagation delays between BS and U1, U2 respectively. Since the UL OFDM symbol has to reach BS with same timing, each user has to transmit the UL signal in advance timing as shown in the figure. The BS measures the UL arrival signal timing from each user and gives feedback to each user. This timing measurement will be further explained in Section 18.4.5.

Figure 18.13 TDD frame and GAP.

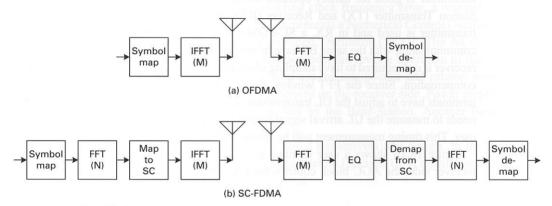

Figure 18.14 Simplified OFDMA and SC-FDMA.

#### 18.2.8.2 SC-FDMA transceiver overview

One well-known problem of OFDM/OFDMA is large peak-to-average power ratio (PAPR), since the transmit waveform is generated by IFFT of many complex digital modulation symbols. The large PAPR needs a wide range of linearity in the transmission power amplifier and causes higher power dissipation at the transmitter. Especially, this will be a problem in battery operated handsets. A SC-FDMA (Single-Carrier Frequency Division Multiple Access) system tries to reduce PAPR while using the same OFDMA frequency domain equalization technique. Figure 18.14 shows a comparison between OFDMA and SC-FDMA systems. In the OFDMA system, bit information is mapped to complex digital modulation symbols such as QPSK/16QAM/64QAM constellation. Then the output of IFFT might have large peak value. In the SC-FDMA system, bit

information is mapped to complex digital modulation symbols and the N symbols are processed by N-points FFT. The N-points FFT outputs are bundled to a block. Then the K blocks are connected and mapped to M-points IFFT inputs. Here, assume  $M = N \times K$ . In this mapping process, each block corresponds to different subcarrier frequencies. Consequently, at the output of M-points IFFT is a sum of frequency shifted N-FFT input sets. Since the input of N-FFT is determined by complex digital modulation symbols, the PAPR of M-IFFT output is reduced. Please note that GI is also used in SC-FDMA although it is not indicated in Figure 18.14.

In other words, SC-FDMA uses Spread Spectrum method by *N*-FFT. Then the spread spectrum is assigned onto many subcarrier frequencies and transmitted parallel in channel. At the receiver, frequency domain channel estimation and equalization is performed. Then the spread spectrum is re-converted to original complex digital modulation symbols by *N*-IFFT. The mapping process between *N*-FFT and *M*-IFFT is equivalent to assigning frequency bands to the spread spectrums.

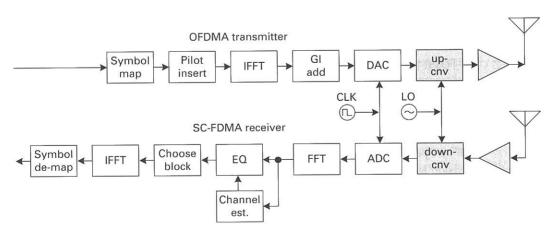

#### 18.2.8.3 OFDMA transceiver architecture

In this section, OFDMA downlink and SC-FDMA uplink are assumed since a SC-FDMA transmitter is good for battery-operated mobile terminals. Figure 18.15 shows a Base-Station Transmitter (TX) and Receiver (RX) block diagram. In the TX, an OFDMA transmitter is used and in RX, a SC-FDMA receiver is used. Since all user terminals communicating with the same BS have to synchronize to the Base-Station, a Base-Station receiver is not required to have sampling clock frequency error compensation and RF error compensation. Since the FFT window position timing is determined in a BS, all user terminals have to adjust the UL transmission timing by the control of the BS. Then the BS needs to measure the UL arrival signal timing from each user and gives feedback to each user. This timing measurement will be further explained in Section 18.4.5.

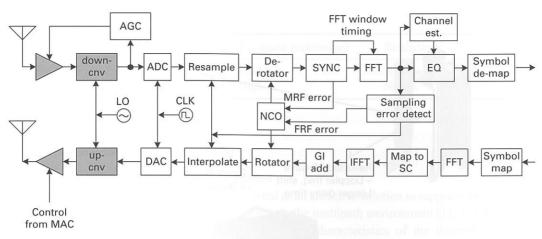

Figure 18.16 shows a user terminal transmitter and receiver block diagram. In the receiver side, the AGC block controls the LNA in the analog front-end. There are two

Figure 18.15 Base-station TX and RX.

Figure 18.16 User terminal TX and RX.

local oscillators. One is for RF conversion and the other is for ADC/DAC. In order to compensate for the RF error and sampling clock frequency error, a resampler and derotator are required. In the figure, NCO represents a Numerical Control Oscillator, which is the digital form of a Voltage Controlled Oscillator (VCO). The NCO frequency corresponds to RF error. In the transmitter side, the reverse operation of the resampler and the de-rotator are required and these are the interpolator and rotator, respectively. Control signals for those blocks are generated on the receiver side. Power amplifier (PA) gain in the analog front-end is controlled by the Base-Station. Another Base-Station control item is UL start timing.

We have discussed various OFDM-based transceivers and design. In the following sections, related error detection and compensation (Section 18.4) together with diversity techniques (Section 18.3) will be addressed.

#### 18.3 Adaptive antenna array and diversity

#### 18.3.1 Introduction to multiple antenna receivers

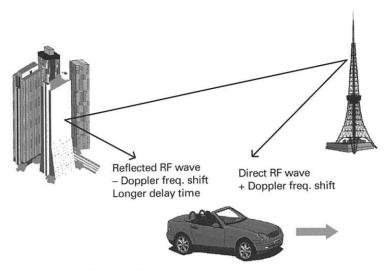

When an OFDM receiver is used in moving vehicles such as automobiles etc., the radio frequency wave suffers from Doppler frequency shift as the automobile is moving as shown in Figure 18.17. The Doppler shift destroys the orthogonality between OFDM subcarrier signals and increases the inter carrier interference. A longer multipath might cause inter symbol interference and weak reception signal power might decrease signal-to-noise ratio (SNR) so as to degrade the reception performance. Therefore, it is a severe challenge to maintain the reception quality in mobility circumstances.

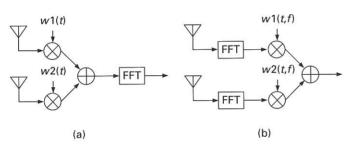

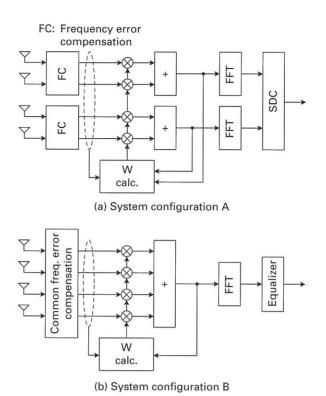

One well-known way to improve the performance of an OFDM receiver is to exploit a spatial diversity by utilizing multiple antenna elements. There are two approaches to utilizing array antenna for the multi-carrier transmission method, which are pre-FFT

Figure 18.17 Problems in mobile reception.

Figure 18.18 Two types of space diversity for OFDM communication.

adaptive array (AA) antenna and post-FFT carrier diversity (CD) combining scheme. The AA scheme is a conventional method to employ the array antenna in which inputs from the array antenna are combined before OFDM demodulation [7–9] as shown in Figure 18.18(a). Since this approach uses one set of coefficients such as w1(t) and w2(t) for each OFDM symbol, it is an attractive solution in term of low computation requirement. However, in order to achieve a good performance, received antenna signals should have higher correlation.

On the other hand, the post-FFT scheme is an advanced method to utilize the array antenna for a multi-carrier system as shown in Figure 18.18(b). Instead of combining before OFDM demodulation, inputs are demodulated using multiple OFDM demodulations. Subcarriers are then combined accordingly in the frequency domain using a diversity combining method [10]. The post-FFT scheme therefore is an optimum approach in term of maximizing SNR for each OFDM subcarriers. However, its computation complexity grows drastically as more antenna elements are associated. The features of the two diversity methods are summarized in Table 18.3.

| Туре                   | Circuit size | Reception performance | Restriction                     |

|------------------------|--------------|-----------------------|---------------------------------|

| Adaptive Array (AA)    | Small        | Moderate              | High antenna signal correlation |

| Carrier Diversity (CD) | Large        | High                  | NONE                            |

Table 18.3 Features of two diversities.

#### 18.3.2 Time-domain diversity

#### 18.3.2.1 OFDM-directed array antenna system

An adaptive array antenna is considered as an attractive solution to suppress interferences and to enhance the quality of reception in the multipath environment [11, 12]. It usually requires in advance the knowledge of the characteristics of the desired signals to distinguish between them and undesired signals. However, due to their high complexity, these approaches are costly in terms of computation effort and hardware implementation. In this section, OFDM-directed two array antenna Digital Beam-Forming (DBF) algorithms with lower computation requirements are introduced. The DBF algorithms make use of the cyclic prefix's periodic property. Figure 18.19(a) and (b) illustrate the periodic property of the OFDM signal and the principle of the time-domain adaptive array antenna system. For convenience, here, the GI with duration of  $T_g$  is referred to as "HeadGI" and the last part of the effective OFDM symbol with duration of  $T_g$  is referred to as "TailGI."

Suppose that an array antenna is equipped with M elements. The vector input signals of the array antenna can be expressed as

$$\mathbf{X}(t) = [x_1(t)x_2(t)\dots x_M(t)]^T$$

=  $\mathbf{V}_s s(t) + \mathbf{V}_i i(t) + \mathbf{N}(t)$  (18.22)

where superscript [.]<sup>T</sup> denotes a transpose of the matrix; s(t) and i(t) are the desired signal and interference, respectively;  $\mathbf{V}_s$  and  $\mathbf{V}_i$  are the array response vectors of the desired signal and interference, respectively;  $\mathbf{N}(t)$  is the AWGN (additive white Gaussion noise) vector of the array antenna. Hence, the output of the array antenna system is calculated as follows

$$y(t) = \mathbf{W}^{H} \mathbf{X}(t)$$

$$= \mathbf{W}^{H} \mathbf{V}_{s} s(t) + \mathbf{W}^{H} \mathbf{V}_{i} i(t) + \mathbf{W}^{H} \mathbf{N}(t)$$

$$= a_{s} s(t) + a_{i} i(t) + n(t)$$

(18.23)

where superscript [.]<sup>H</sup> denotes Hermitian;  $\mathbf{W} = [w_1 \ w_2 \dots w_M]^T$  is the coefficient vector of the array antenna;  $a_s = \mathbf{W}^H \mathbf{V}_s$  and  $a_i = \mathbf{W}^H \mathbf{V}_i$  are constant during one OFDM symbol.

In references [13–14], the conventional Maximum Ration Combining (MRC) algorithm is derived directly from the cross-correlation of inputs and outputs of the array antenna:

$$\mathbf{W}_{convMRC} = E[\mathbf{X}(t)y^{*}(t)]$$

$$= E[(\mathbf{V}_{s}s(t) + \mathbf{V}_{i}i(t) + \mathbf{N}(t))(a_{s}s(t) + a_{i}i(t) + n(t))^{*}]$$

$$= a_{s}^{*}P_{s}\mathbf{V}_{s} + a_{i}^{*}P_{i}\mathbf{V}_{i}$$

(18.24)

where  $P_s = E[|s(t)|^2]$  and  $P_i = E[|i(t)|^2]$ . Superscript (.)\* denotes complex conjugate. Apparently from Equation (18.24), the array antenna utilizing the conventional MRC combines not only the desired signal but also the interference. Under the circumstances that the power of interference is stronger than that of the desired signal, the interference will be emphasized at the output of the array antenna.

#### 18.3.2.2 OFDM selective Maximum Ration Combining (MRC)

In order to overcome the limitation of the conventional MRC method described above, by making use of HeadGI of input and feedback of TailGI of output, the cross-correlation of input and output is derived as

$$\mathbf{r}_{xy} = E[\mathbf{X}_h(t)y_t^*(t)] = E[(\mathbf{V}_s s_h(t) + \mathbf{V}_i i_h(t) + \mathbf{N}_h(t))(a_s s_t(t) + a_i i_t(t) + n_t(t))^*] = a_s^* \mathbf{V}_s E[s_h(t)s_t^*(t)] + a_i^* \mathbf{V}_i E[i_h(t)i_t^*(t)]$$

(18.25)

Figure 18.19 (a) Cyclic properties of OFDM signal and (b) Adaptive array using GI.

where subscripts (.)<sub>h</sub> and (.)<sub>t</sub> denote HeadGI and TailGI of the signal, respectively. Since i(t) is interference and does not have cyclic prefix GI, the second term of Equation (18.25) can be neglected. Employing the periodic property of OFDM signal, Equation (18.25) can be expressed as follows:

$$\mathbf{r}_{xy} = a_s^* \mathbf{P}_s \mathbf{V}_s. \tag{18.26}$$

Hence, Equation (18.26) presents the information of AOA (angle of arrival) of the desired signal without the reference signals. Therefore, the coefficient vector of the array antenna using MRC algorithm is derived as below. In other words, this OFDM selective MRC algorithm is beam-forming only to OFDM signals

$$\mathbf{W}_{MRC} = \text{normalize}(\mathbf{r}_{xy}). \tag{18.27}$$

#### 18.3.2.3 Minimum Mean Square Error (MMSE) and Sampled Matrix Inversion (SMI)

Although the OFDM selective MRC algorithm emphasizes the desired OFDM signal, it does not minimize the interference. In this section, the Minimum Mean Square Error (MMSE) algorithm is derived. Assume a reference signal is r(t). The error signal is given as:

$$e(t) = r(t) - \mathbf{W}^{\mathsf{H}} \mathbf{X}(t). \tag{18.28}$$

The MSE (mean square error) between the output of the array antenna and the reference signal is given as:

$$MSE = E[|e(t)|^{2}] = E[|e(t)r(t) - \mathbf{W}^{H}\mathbf{X}(t)|^{2}].$$

(18.29)

By minimizing the MSE with the well-known Wiener-Hoff equation, the optimum coefficients are derived as

$$\mathbf{W}_{MMSE} = \text{normalize}(\mathbf{R}_{xx}^{-1}\mathbf{r}_{xy})$$

(18.30)

where  $\mathbf{R}_{xx} = E[\mathbf{X}_h \mathbf{X}_h^H]$  is the autocorrelation matrix of inputs. In real applications,  $\mathbf{R}_{xx}$  can be obtained by a simple averaging scheme [15]. According to Equation (18.30), the additional calculation of the inverse of  $\mathbf{R}_{xx}$  makes MMSE possible and then this algorithm is also called Sampled Matrix Inversion (SMI).

#### 18.3.3 Frequency-domain diversity

#### 18.3.3.1 MRC for uniformly distributed branch noise

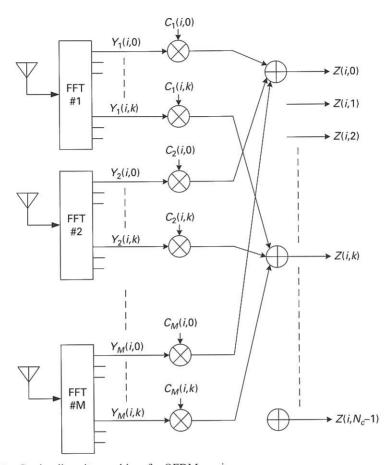

Figure 18.20 illustrates the post-FFT carrier diversity (CD) combiner for an OFDM receiver. This system assumes there are M antennas and M OFDM demodulations. The combined symbol at the kth subcarrier of the ith OFDM symbol is given as

$$Z(i,k) = \sum_{l=1}^{M} C_l(i,k) Y_l(i,k)$$

(18.31)

Figure 18.20 Carrier diversity combiner for OFDM receiver.

where  $C_l(i,k)$  and  $Y_l(i,k)$  are the combining coefficient and the demodulated symbol corresponding to the *l*th branch of the combiner at the *k*th subcarrier of the *i*th OFDM symbol, respectively. Here, the following equation is assumed

$$Y_l(i,k) = H_l(i,k)d(i,k) + N_{Bl}(i,k)$$

(18.32)

where  $H_l(i,k)$ ,  $N_{Bl}(i,k)$  are the channel transfer function and the additive noise corresponding to the lth branch of the combiner at the kth subcarrier of the ith OFDM symbol, respectively and d(i,k) is the transmitted complex digital modulation symbol at the kth subcarrier of the ith OFDM symbol. According to Reference [10], the combining coefficients for the MRC algorithm can be obtained as follows

$$C_l(i,k) = \frac{H_l^*(i,k)}{\sum_{l=1}^{M} |H_l(i,k)|^2}$$

(18.33)

where assuming that the mean of  $N_{Bl}(i,k)=0$  for all l, i, k and the deviation of  $N_{Bl}(i,k)$  are all the same for all l, i, k. By using the MRC algorithm, the

Figure 18.21 Multiple antennas of a car.

optimum combined output SNR can be achieved for each subcarrier by post-FFT CD scheme.

#### 18.3.3.2 MRC for independently distributed branch noise

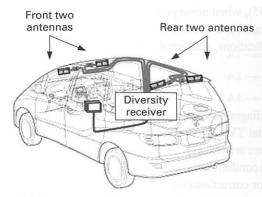

When one antenna of the receiver is broken or hidden, the noise of the branch increases and has impact on the combined output. Figure 18.21 shows a typical 4 space diversity antenna configuration for an automobile. Two antenna elements are set in the front and two are set in the rear. However as the body of the automobile is made from metal, the directional characteristics of the front antenna is obviously distorted and concentrates in the forward direction. Then, the uniform noise power distribution assumed in the previous section sometimes cannot be applied to these kinds of unbalanced antenna situations.

Equation (18.33) can be rewritten as:

$$C_{l}(i,k) = \frac{H_{l}^{*}(i,k)}{|H_{l}(i,k)|^{2}} \cdot \frac{|H_{l}(i,k)|^{2}}{\sum_{l=1}^{M} |H_{l}(i,k)|^{2}}$$

$$= \frac{1}{H_{l}(i,k)} \cdot \frac{|H_{l}(i,k)|^{2}}{|H_{1}(i,k)|^{2} + \dots + |H_{M}(i,k)|^{2}}$$

(18.34)

The first division by  $H_l(i,k)$  corresponds to the equalizing operation. The second multiplication term means how much branch l contributes to combining. Since  $H_l(i,k)$  is CTF, then it corresponds to the signal gain in the transmission channel. If the average noise power of each branch (l = 1 ... M) is denoted by  $\sigma^2_{nl}$ , the above equation can be modified to the following equation (18.35), which is taking noise distribution between branches into account.

$$C_{l}(i,k) = \frac{1}{H_{l}(i,k)} \cdot \frac{|H_{l}(i,k)|^{2}/\sigma_{nl}^{2}}{|H_{1}(i,k)|^{2}/\sigma_{n1}^{2} + |H_{2}(i,k)|^{2}/\sigma_{n2}^{2} + \dots + |H_{M}(i,k)|^{2}/\sigma_{nM}^{2}}$$

(18.35)

According to Equation (18.35), when noise power at branch 1 increases, the combining coefficients  $C_l(i,k)$  become small and will contribute less to the combining. When using Equation (18.35) in real applications, additional noise power estimation is needed.

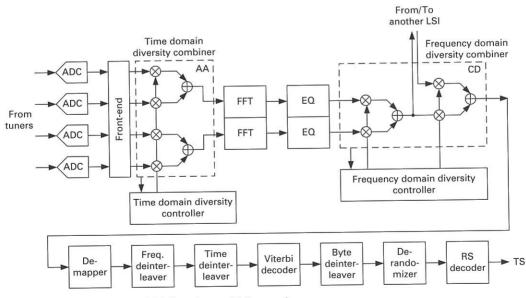

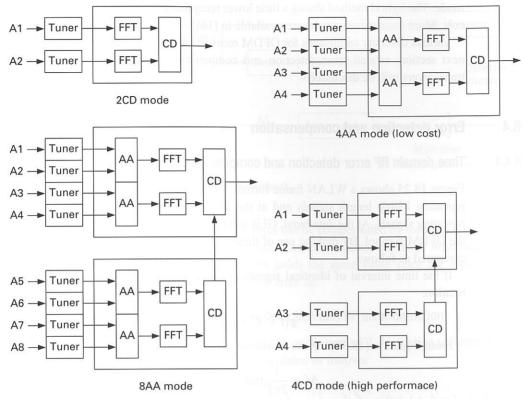

#### 18.3.4 Hybrid diversity

Figure 18.22 shows a block diagram of a four antenna diversity combining receiver LSI for Japan OFDM-based Digital TV [16]. In the first stage, two sets of two antenna MRC combiners are used. Then there are two sets of FFT and Equalizer circuits. In the second stage, the two EQ outputs are combined as a carrier diversity method. The final combined output is de-mapped and error correction processing is applied. The two stage diversity combiners halve the number of FFT/EQ circuits from four to two and sustain a similar mobile reception performance comparing with the four FFT/EQs case. In the second CD stage, another LSI interface is prepared and then in total four kinds of diversity configurations are possible as shown in Figure 18.23.

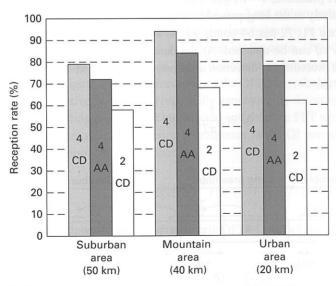

Mobile reception performance was measured by field experiment at three severe test courses in Osaka Japan for 4CD, 4AA, 2CD configurations. The experimented UHF channel is 13ch which is broadcasted from the top of IKOMA Mountain between Osaka and Nara prefecture. 64QAM, code rate of 3/4, 12 segments HDTV broadcasting service are used. The three test courses are a suburban area 50 km from IKOMA broadcasting station (BS), a mountain area 40 km from BS, and an urban area but in the shadow of a hill 20 km from BS. Figure 18.24 shows the reception rate (the rate of the error free reception duration to the total experiment duration) of those test courses. One chip solution 4AA mode showed a little lower performance than the two chip solution 4CD

Figure 18.22 Four antenna hybrid diversity combining receiver.

Figure 18.23 Four possible diversity configurations.

Figure 18.24 Field experimental results.

mode. The hybrid method shows a little lower reception performance with lower system cost. More comparison results are available in [16].

Various diversity techniques for OFDM receivers are addressed in this section. In the next section, related error detection and compensation techniques for OFDM-based transceivers will be discussed.

#### 18.4 Error detection and compensation

#### 18.4.1 Time domain RF error detection and compensation

Figure 18.25 shows a WLAN frame format. At the short preamble period, there are 10 repeating  $1/(4f_0)$  length signals and at the long preamble, T1 and T2 are  $1/f_0$  length repeating signals. At the data burst, GI is a cyclic prefix, that is, a copy of the tail part of the OFDM symbol. By making use of these repeating or copy signals, RF error can be computed as follows.

If the time interval of identical signals g(t) and g(t+T) is T, RF error  $\Delta f$  causes the rotation:

$$g(t+T) = g(t)e^{j2\pi\Delta fT}.$$

(18.36)

From Equation (18.36),  $\Delta f$  can be solved as follows:

$$\Delta f = \frac{1}{2\pi T} \tan^{-1} [g(t+T)g^*(t)]$$

(18.37)

$$-\frac{1}{4T} < \Delta f < \frac{1}{4T}.\tag{18.38}$$

At the short preamble,  $T = 1/(4f_0)$ . Then, RF error  $\Delta f$  in the region  $[-f_0, f_0]$  can be detected. Similarly at the long preamble region,  $\Delta f$  in the region of  $[-f_0/4, f_0/4]$  can be estimated. Since T1, T2 has 64 points whose average reduces the  $\Delta f$  detection error, a high accuracy  $\Delta f$  can be obtained. At the data burst region,  $\Delta f$  should be very small because of the preceding  $\Delta f$  detection and compensation. Then Equation (18.37) can be approximated as:

$$\Delta f \cong \frac{1}{2\pi T} \operatorname{Im}[g(t+T)g^*(t)]. \tag{18.39}$$

Figure 18.25 Time domain RF error detection.

Figure 18.26 Time domain RF error compensation feedback.

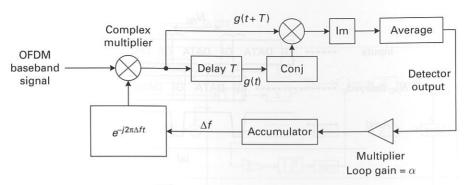

During the data burst region, RF error can be compensated by feedback loop as shown in Figure 18.26. In the loop, loop gain  $\alpha$  and accumulator are used. When the RF error detector output = 0, the accumulator holds the same value since the input = 0. The accumulator output corresponds to RF error  $\Delta f$ .

#### 18.4.2 Time domain FFT window position detection and RF error detection

The FFT window position can be found by cyclic prefix GI. According to Reference [17], head and tail GI correlation can be calculated as follows:

$$As(k) = \sum_{i=0}^{M-1} \left\{ |r(k+i)|^2 + |r(k+i+N_{PD})|^2 \right\} - 2 \left| \sum_{i=0}^{M-1} r(k+i+N_{PD}) \cdot r^*(k+i) \right|$$

(18.40)

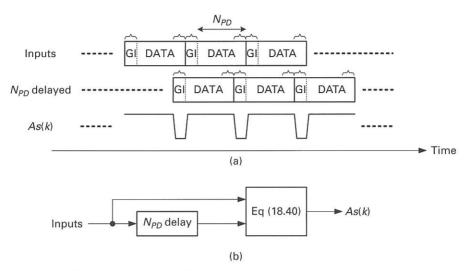

where r(k) is the baseband OFDM signal input. Index i is used to average M points. If the time index k is not in the GI period,  $r(k+N_{PD})$  and r(k) are independent. Then the second term will be close to zero. Instead, if the time index k is in the GI period,  $r(k+N_{PD})$  and r(k) should be close. Then the output of Equation (18.40) will be close to zero. Consequently, the correlation As(k) waveform is negative pulse at the GI period as shown in Figure 18.27(a). Here,  $N_{PD}$  is the OFDM symbol length.

The negative pulse will be repeatedly generated. By detecting the pulse rising edge, the OFDM starting position can be detected and then the FFT window position is obtained. Since the negative pulse period corresponds to the GI period, phase rotation  $\varphi$  in one OFDM symbol can be obtained as:

$$\varphi = \text{angle} \left\{ \sum_{i=0}^{M-1} r(k+i+N_{PD}) \cdot r^*(k+i) \right\}.$$

(18.41)

Since the phase rotation  $\varphi$  happens in OFDM symbol period (1/ $f_0$ ), the RF error  $\Delta f$  can be calculated as follows

$$\Delta f = \frac{\varphi}{2\pi} f_0. \tag{18.42}$$

Figure 18.27 Cyclic prefix GI time domain correlation.

**Figure 18.28** Phase rotation with RF error  $\alpha$  and sampling clock error  $\beta$ .

### 18.4.3 Time domain RF error, sampling error, and symbol timing detection and compensation

One subcarrier signal with index of n can be expressed as

$$x_n(t) = d_n \cdot e^{j2\pi n f_0 t} \tag{18.43}$$

where  $d_n$  is the *n*th digital modulation symbol and  $f_0$  is the carrier spacing. Then t = 0 for  $1/f_0$  rotation with RF error  $\Delta f$  and the sampling clock error  $\beta$  is can expressed as follows:

$$\frac{X_n\left(\frac{1}{f_0}\right)}{X_n(0)} = e^{\frac{j2\pi(nf_0 + Af)(1-\beta)}{f_0}}$$

$$\cong e^{j2\pi(\alpha - n\beta)}.$$

(18.44)

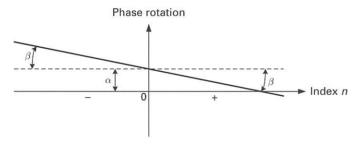

Here  $\alpha$  is the normalized RF error of  $\Delta f/f_0$ . According to Equation (18.44), the RF error causes common phase rotation but the sampling clock error  $\beta$  causes the phase error in proportion to the subcarrier index number n as shown in Figure 18.28.

Figure 18.29 Time domain RF error and sampling clock error compensation.

Then by averaging all phase rotation for all subcarriers, the RF error  $\alpha$  can be obtained. By calculating the phase error in positive frequency (n>0) and phase error in negative frequency (n<0), the sampling clock error  $\beta$  can be calculated.

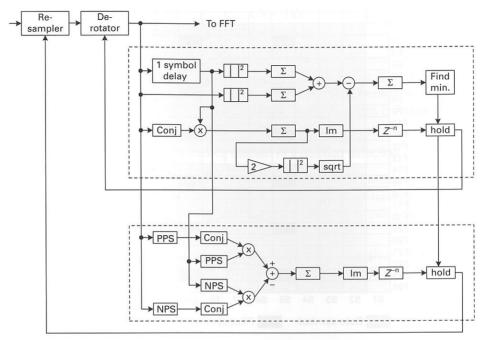

Figure 18.29 shows one example of time domain GI correlation, an RF error detection and sampling clock error detection circuit diagram. The "Find min." block detects minimum points of GI correlation given in Equation (18.40). The upper dashed block outputs RF error and the lower dashed block outputs sampling clock error. PPS and NPS represent positive and negative pass FIR filters, respectively. Since they form a feedback loop and the detection error should be close to zero in converged stable state, the imaginary components of the phase errors are used to feedback outputs. The simplest implementation of PPS and NPS FIR filters' tap coefficients are given as [-j, 1, j] and [j, 1, -j] respectively. Here, j represents the square root of (-1).

#### 18.4.4 Frequency domain RF error and sampling error detection

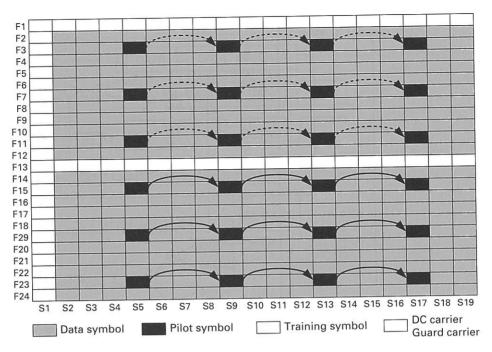

Figure 18.30 shows one Physical Resource Unit (PRU) of an OFDMA-based XGP communication system [4]. It corresponds to 19 OFDM symbols and 24 subcarriers. In one PRU, there are 24 pilots, which transmit pre-determined value. For the same subcarrier number such as F3, F7 and so on, the pilot values are identical and then the phase rotation shown in solid or dashed arrows can be detected. In one PRU, there are 18 phase rotations. The averages of the phase rotation in the lower frequency side (shown in dashed arrows) and in the higher frequency side (shown in solid arrows) can be expressed as follows:

Figure 18.30 XGP PRU structure.

LowRotMean =

$$\frac{p(F3,S5)^* \times p(F3,S9) + \dots + p(F11,S13)^* \times p(F11,S17)}{9}$$

(18.45)

HighRotMean =

$$\frac{p(F15, S5)^* \times p(F15, S9) + \dots + p(F23, S13)^* \times p(F23, S17)}{9}$$

(18.46)

where p(F,S) means the pilot subcarrier value at subcarrier of F and symbol number of S. If we define LV and HV as

$$LV = \frac{imag(LowRotMean)}{real(LowRotMean)}$$

(18.47)

$$HV = \frac{\text{imag(HighRotMean)}}{\text{real(HighRotMean)}},$$

(18.48)

the RF error FRF in Equation (18.49) and sampling clock error CLKD in Equation (18.50) can be calculated:

$$FRF = \frac{m \cdot LV - n \cdot HV}{\frac{9}{4}\pi(m-n)}$$

(18.49)

$$CLKD = \frac{LV - HV}{\frac{9}{4}\pi(m-n)}$$

(18.50)

where *n* and *m* are the center carrier index numbers at the lower frequency side and higher frequency side, respectively. The idea of the calculation is based on the property that RF error rotates the same phase for all subcarriers and that sampling clock error rotates each subcarrier phase in proportion to the carrier number index as shown in Figure 18.28.

#### 18.4.5 Delay profile detection and frequency domain FFT position detection

In the frequency domain, from series of pilot or training symbols, the delay profile can be easily obtained. The S1 symbols of PRU shown in Figure 18.30 are training symbols and their values are all pre-determined. Then by IFFT calculation, delay profile can be obtained as follows:

Delay Profile = IFFT

$$\left[0, \frac{X(F2)}{T(F2)}, \frac{X(F3)}{T(F3)}, \dots, \frac{X(F12)}{T(F12)}, 0, \frac{X(F14)}{T(F14)}, \frac{X(F15)}{T(F15)}, \dots \right]$$

$$\frac{X(F24)}{T(F24)}, 0, \dots, 0$$

(18.51)

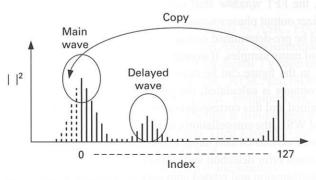

where X(F) is the FFT output of subcarrier F and symbols S1, and T(F) is the predetermined training value at subcarrier F and symbols S1. Then the power profile can be obtained as shown in Figure 18.31. In this profile, the power of the main wave is at index = 0 and then the FFT window position is placed at the main wave position. Because of the cyclic property of IFFT and FFT, the tail profile is connecting to the head profile as shown in Figure 18.31.

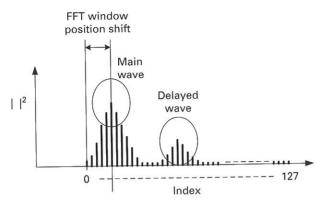

If the FFT window position shifts ahead, the delay profile shifts backward as shown in Figure 18.32. According to the index number of the peak point of delay profile, the FFT window shift can be detected. Detectable maximum delay is the OFDM symbol length divided by the training subcarrier interval. Since the S1 symbol includes all training symbols and its interval equals unity, the detectable maximum delay is the same as the

Figure 18.31 Power delay profile.

Figure 18.32 FFT window position shift ahead.

OFDM symbol length. If pilots in S5 are used to calculate the delay profile, the detectable maximum delay is 1/4 of the OFDM symbol because the pilot interval = 4.

#### 18.4.6 FFT window shift detection by constellation rotation and compensation

A subcarrier signal of index = n can be expressed as Equation (18.52) in one OFDM symbol [0  $1/f_0$ ]. The FFT output of the OFDM symbol with index = n is  $d_n$ .

$$x_n(t) = d_n \cdot e^{j2\pi n f_0 t} \tag{18.52}$$

When the FFT window shifts k points (-0.5 < k < 0.5) forward, the equivalent time shift  $\Delta t$  is

$$\Delta t = \frac{k}{Nf_0}. ag{18.53}$$

Then the FFT output of the OFDM symbol with index = n will become

$$d_n \cdot e^{j2\pi \frac{nk}{N}} \tag{18.54}$$

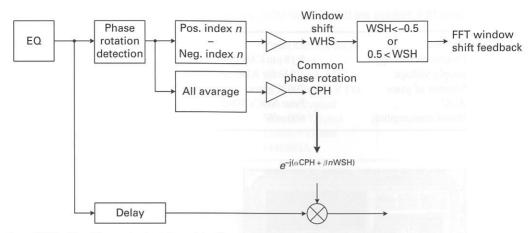

where N is the size of the FFT. This means that the FFT window shift causes a constellation rotation proportional to the index number n. Then by detecting the equalizer output's rotation, the FFT window shift can be detected. Figure 18.33 shows a block diagram of equalizer output phase rotation detection and compensation. Since the equalizer output should be pre-determined constellation based, phase rotation can be detected with the average of many samples. If averaging all the points is performed, the common phase error CPH in the figure can be detected. If the difference between positive and negative index averages is calculated, the phase rotation which is proportional to the index will be obtained and this corresponds to the FFT window shift WSH in the figure. By using CPH and WSH, the constellation can be compensated as shown in Figure 18.33.

We have discussed various OFDM based transceivers and their design, various diversity techniques, and related error detection and compensation techniques. In the final section, the hardware implementation and related chip performance will be addressed.

Figure 18.33 Equalizer output rotation detection and compensation.

Figure 18.34 Block diagram of 4 antennas adaptive combiner LSI.

#### 18.5 Hardware implementation and system integration

#### 18.5.1 Four antenna adaptive array combiner LSI [7]

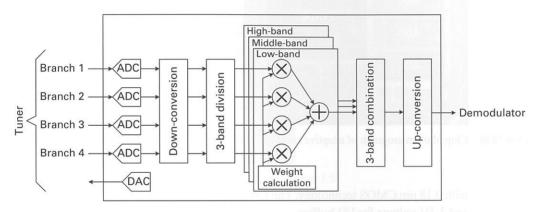

In this section, some implementation results by ASIC, FPGA, and DSP devices will be shown. The first implementation result is ASIC implementation of four antenna adaptive array combiner with MRC algorithm for digital TV receivers. This LSI can be used for 6 MHz bandwidth receivers such as NTSC, ATSC, and ISDB-T. One feature of this LSI is that three independent four antenna MRC combiners are included because the 6 MHz bandwidth is wide. The 6 MHz bandwidth is divided into three 2 MHz bandwidth and a MRC combining process is performed. Then 3-band division and combination circuit are also integrated as shown in Figure 18.34.

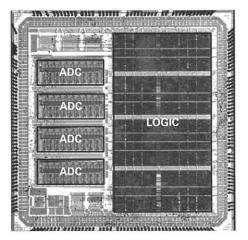

Table 18.4 summarizes the features of the adaptive combiner LSI. Total logic gate size is 700K gates and four analog-to-digital converters are integrated in 25 mm<sup>2</sup> LSI chip

Table 18.4 Features and Data of LSI.

Die size 25 mm<sup>2</sup>

Process technology 0.18 µm CMOS 6-metal

Supply voltage 1.8 V for ADC and Logic 3.3 V for IO buffer

Number of gates 700 K gates

ADC Four ADCs 10bits 33 Msps

Power consumption 600 mW

Figure 18.35 Chip photomicrograph of adaptive combiner LSI.

with  $0.18 \,\mu m$  CMOS technology. The LSI needs 1.8 V voltage supply for internal circuits and 3.3 V voltage for I/O buffers.

In this implementation, four ADCs need approximately 25 percent of die area with 0.18 µm CMOS technology. A chip photomicrograph is shown in Figure 18.35.

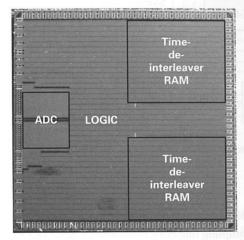

#### 18.5.2 A 2/4/8 Antennas Configurable Diversity OFDM Receiver LSI [16]

The second implementation result is a 2/4/8 Antennas Configurable Diversity OFDM Receiver LSI for Japan digital TV specification of ISDB-T. The LSI is composed of time domain adaptive array and frequency domain carrier diversity as shown in Figure 18.22. Using one or two LSIs, 2/4/8 antennas diversity configurations are possible as shown in Figure 18.23. In addition to OFDM demodulation, the LSI integrates Viterbi and Reed-Solomon Error correction circuits.

The features of the diversity receiver LSI is shown in Table 18.5. The LSI integrates 4 ADCs, 1.8 M gates and 18.4 Mbit SRAM memory in 49 mm<sup>2</sup> with 90 nm CMOS technology. The largest memory is time de-interleave RAMs because of the ISDB-T requirement. The core logic supply voltage is 1.2V and I/O circuit needs 3.3 V supply voltage. A chip photomicrograph is shown in Figure 18.36.

Table 18.5 Features and data of Diversity OFDM Receiver LSI.

| Process technology | 90 nm 7M1P CMOS                      |  |

|--------------------|--------------------------------------|--|

| Logic              | 1.8 M gates                          |  |

| Memory and ADC     | 18.4 M bit/4 ADC                     |  |

| Supply voltage     | 1.2 V core, 3.3 V I/O                |  |

| Active power       | 310 mW typical                       |  |

| Die size           | $7.0\mathrm{mm}\times7.0\mathrm{mm}$ |  |

|                    | 12 mm × 12 mm                        |  |

| Package            | 144FBGA                              |  |

Figure 18.36 Chip photomicrograph of Diversity OFDM receiver LSI.

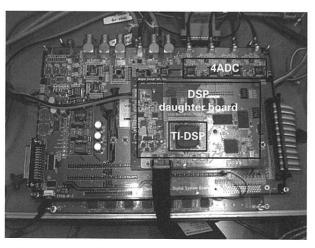

# 18.5.3 Joint hardware-software implementation of adaptive array antenna OFDM receiver by FPGA [9]

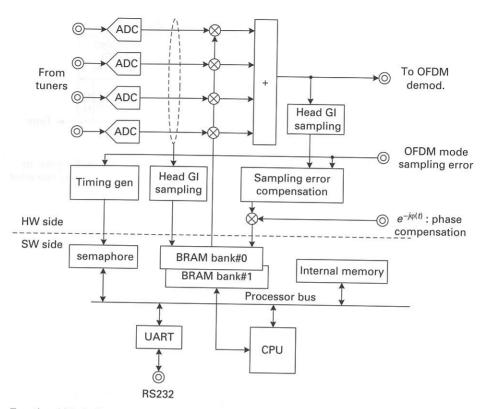

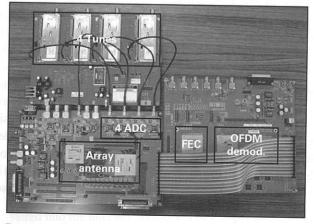

Figure 18.37 illustrates a block diagram of the array antenna concatenating with a OFDM demodulator. A digital beamforming (DBF) algorithm to generate the coefficients of the array antenna is executed prior to FFT. The output of the array antenna is fed to the OFDM demodulator to retrieve the transmitted data. A joint hardware-software (HW-SW) solution is chosen to provide an easily debugged and flexible platform for adaptive array antenna processing. The supported adaptive array antenna algorithms are OFDM selective Maximum Ration Combining (MRC) as in Section 18.3.2.2 and Sample Matrix Inversion (SMI) as in Section 18.3.2.3.

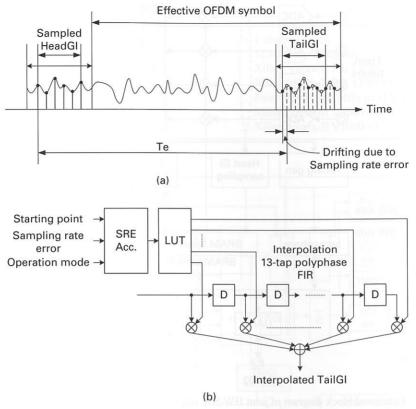

Since RF error and sampling rate error are inherently unavoidable, the compensation feedback signals of RF error and sampling error are provided from OFDM demodulator to array antenna signal processing. Figure 18.38(a) shows an impact of sampling rate error on a sampled TailGI. Due to the drifting of the sampling portion of TailGI, the samples of TailGI do not remain precisely. Therefore, it obviously deteriorates the

Figure 18.37 Block diagram of adaptive array antenna OFDM receiver (where "RE-SE-C" stands for "RF error and Sampling error compensator")

cross-correlation between HeadGI of the inputs and TailGI of the output. The block diagram of the compensator of sampling rate error is shown in Figure 18.38(b). The error is estimated in the OFDM demodulator and accumulated on each OFDM symbol to measure the exact duration of effective symbol length  $T_e$ . TailGI is then fed to a 13-tap poly-phase FIR filter to eliminate the impact of sampling rate error. The coefficients of the 13-tap FIR filter are determined by the value of the  $T_e$  using an LUT method (Look-Up Table). Not only RF error and sampling rate error, but also the operation mode of ISDB-T and the synchronization of the OFDM symbol are provided from OFDM demodulation and they are fed back to the adaptive array antenna.