教科書P31 process文を用いた組み合わせ回路

琉球大学情報工学科 和田 知久

process文を用いた組み合わせ回路の記述方法

- 入力信号をもちいて、出力信号の動作のみを記述すればよい。

- process( )の( )内にすべての入力信号を書く。忘れると、かってにフリップフロップが生成される。

- process文内部は順次処理なので、if文、case文、for-loop文を用いることができる。

- process文内部の記述で中間変数が必要であれば、process文内部で variable を宣言して用いる。

- variableは代入式 が TMP := S+D; のように異なるので、注意せよ。(即時代入)

リスト if文の例

|

ライブラリ宣言 |

library IEEE; |

いつもどおり |

|

ENTITY宣言 |

entity MULTIPLEXER4 is |

エンティティ宣言 |

|

port ( D : in std_logic_vector(3

downto 0); |

ポート宣言 |

|

|

end MULTIPLEXER4; |

エンティティ終了。";"忘れるな! |

|

|

回路の中味の記述 |

architecture DATAFLOW of MULTIPLEXER4 is |

アーキテクチャ宣言 |

|

begin |

|

リスト case文の例

|

ライブラリ宣言 |

library IEEE; |

いつもどおり |

|

ENTITY宣言 |

entity DECODER_2_4 is |

エンティティ宣言 |

|

port ( D : in std_logic_vector(1

downto 0); |

ポート宣言 |

|

|

end DECODER_2_4; |

エンティティ終了。";"忘れるな! |

|

|

回路の中味の記述 |

architecture DATAFLOW of DECODER_2_4 is |

アーキテクチャ宣言 |

|

begin |

|

リストfor-loop文の例

|

ライブラリ宣言 |

library IEEE; |

いつもどおり |

|

ENTITY宣言 |

entity PARITY_CHECKER is |

エンティティ宣言 |

|

port ( A : in std_logic_vector(7

downto 0); |

ポート宣言 |

|

|

end PARITY_CHECKER; |

エンティティ終了。";"忘れるな! |

|

|

回路の中味の記述 |

architecture DATAFLOW of PARITY_CHECKER is |

アーキテクチャ宣言 |

|

begin |

|

Variable と Signal (代入が時間的に異なり、トラブリやすい)

- Signalは architecture-begin 間で宣言され、その architectureでのグローバルな変数のやりとりを行う。

- Signalは信号代入文( <= )で代入され、代入はδ(微少)時間後に行われる。

- Variableは process-begin 間で宣言され、そのprocessでのみ有効なローカルな変数となる。

- Variableは変数代入文( := )で即座に代入される。

|

architecture RTL of REI is process (X, Y, Z, C) begin C <= Z; end process; この例ではCにY,Zが代入されるが、それらは A <= X + Y B <= X + Y |

architecture RTL of REI is process (X, Y, Z) C := Z; end process; この例ではCはvariableであり、その行で A <= X + Z B <= X + Y |

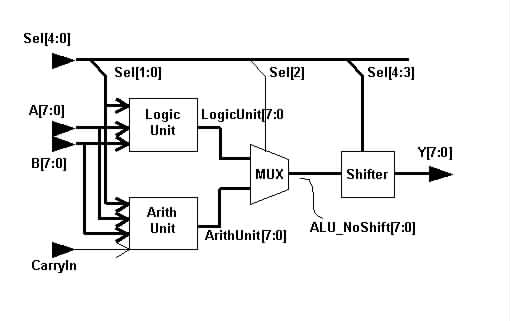

あるarithmetic logic unit (ALU)の設計

- ALUとはセントラルプロセシングユニットCPUのコアで、単なる組み合せ回路にて、算術(加算、減算)や論理演算を行う。

- 以下に14の命令をこなすALUの例を示す。

- 単なる組み合せ回路ということを忘れずに。

|

S4 |

S3 |

S2 |

S1 |

S0 |

Cin |

動作 |

説明 |

実行ブロック |

|

0 |

0 |

0 |

0 |

0 |

0 |

Y <= A |

Aを転送 |

Arithmetic Unit |

|

0 |

0 |

0 |

0 |

0 |

1 |

Y <= A+1 |

Aをインクリメント |

Arithmetic Unit |

|

0 |

0 |

0 |

0 |

1 |

0 |

Y <= A + B |

加算 |

Arithmetic Unit |

|

0 |

0 |

0 |

0 |

1 |

1 |

Y <= A + B + 1 |

キャリー付加算 |

Arithmetic Unit |

|

0 |

0 |

0 |

1 |

0 |

0 |

Y <= A + Bbar |

AとBの1の補数をたす |

Arithmetic Unit |

|

0 |

0 |

0 |

1 |

0 |

1 |

Y <= A + Bbar + 1 |

減算 |

Arithmetic Unit |

|

0 |

0 |

0 |

1 |

1 |

0 |

Y <= A - 1 |

デクリメント |

Arithmetic Unit |

|

0 |

0 |

0 |

1 |

1 |

1 |

Y <= A |

Aを転送 |

Arithmetic Unit |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

0 |

Y <= A and B |

論理積 |

Logic Unit |

|

0 |

0 |

1 |

0 |

1 |

0 |

Y <= A or B |

論理和 |

Logic Unit |

|

0 |

0 |

1 |

1 |

0 |

0 |

Y <= A xor B |

排他的論理和 |

Logic Unit |

|

0 |

0 |

1 |

1 |

1 |

0 |

Y <= Abar |

1の補数 |

Logic Unit |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

Y <= A |

Aを転送 |

Shifter Unit |

|

0 |

1 |

0 |

0 |

0 |

0 |

Y <= shl A |

Aを左シフト |

Shifter Unit |

|

1 |

0 |

0 |

0 |

0 |

0 |

Y <= shr A |

Aを右シフト |

Shifter Unit |

|

1 |

1 |

0 |

0 |

0 |

0 |

Y <= 0 |

0を転送 |

Shifter Unit |

|

ライブラリ宣言 |

library IEEE; |

IEEE.std_logic_unsignedは、std_logic_vector型で |

|

エンティティ |

entity ALU is |

エンティティ宣言 |

|

アーキテクチャ |

architecture COND_DATA_FLOW of ALU is |

内部で直ぐに後段の回路で用いる信号はVariableで宣言する。 |

|

--------------------------- |

LogicUnitは後段で用いるので、Variableとし、即値代入(:=)を使用する。 |

|

|

--------------------------- |

ArithUnitは後段で用いるので、Variableとし、即値代入(:=)を使用する。 |

|

|

--------------------------- |

ALU_NoShiftは後段で用いるので、Variableとし、即値代入(:=)を使用する。 |

|

|

--------------------------- |

出力YはSignalなので、遅延代入(<=)を用いる。 |

|

|

end process

ALU_AND_SHIFT; |

|

実習 ALUの動作シミュレーション(1)

0) 作業ディレクトリに、上記2つのファイルをコピーする。

1)正常動作を確認せよ!

実習

2) 回路合成を行う。

HOMEWORK2

上記ALU回路にて、入力信号A,B、出力信号Yを16ビット化し、

① 動作シミュレーション波形

② 回路合成FINALレポート

③ 回路合成後の、テクノロジースケマティック

を含む、設計レポートを提出せよ。

以上